PT-50LC13

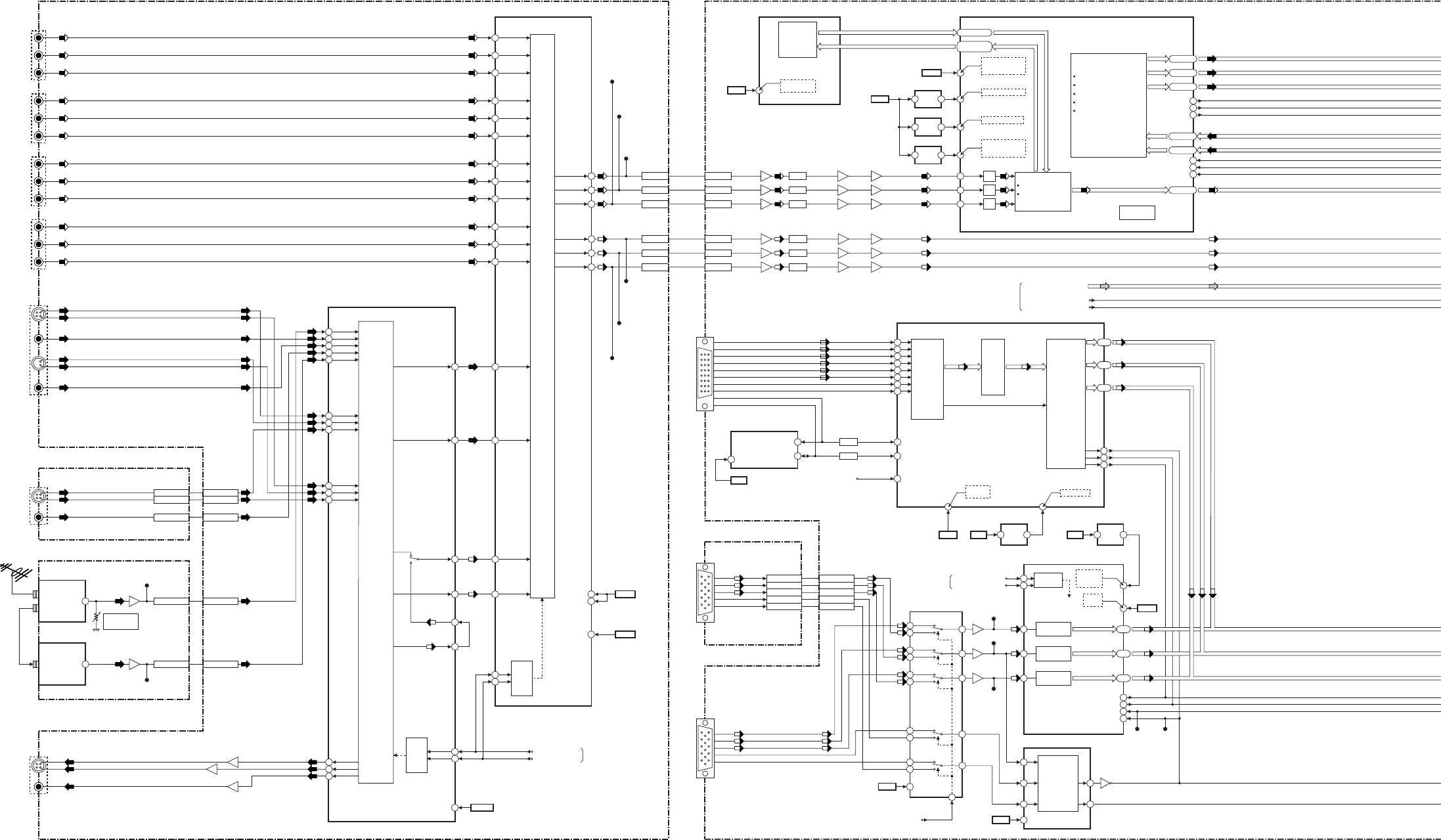

VIDEO SIGNAL PATH I BLOCK DIAGRAM (1/2)

VIDEO SIGNAL PATH I BLOCK DIAGRAM (1/2)

S-VIDEO IN1

VIDEO

RF-IN

RF-OUT

FRONT JACK C.B.A.

TUNER C.B.A.

REAR JACK C.B.A. MAIN C.B.A.

U7001

(MAIN TUNER)

Q7002

Q7101

Q3501

Q3502

Q3503

25

VIDEO IN1

VIDEO IN2

S-VIDEO IN2

IC3501 (AUDIO/VIDEO SW)

IC3602 (SW) IC5005 (MAIN VIDEO SIGNAL PROCESS)

IC5002 (5.6M FIFO MEMORY)

VIDEORF-IN

U7101

(SUB TUNER)

25

P7002-1

FRONT JACK C.B.A.

S-VIDEO IN3

VIDEO IN3

COMPONENT

-Y1

COMPONENT

-PB1

COMPONENT

-PR1

COMPONENT

-Y2

COMPONENT

-PB2

COMPONENT

-PR2

Y

C

Y

C

Y

C

S-VIDEO

OUT

VIDEO OUT

P7002-3 P3501-3

P3501-1

P3502-7

P3502-5

P3502-3

P3902-7

P3601-18

MAIN Y/V

MAIN PB/C

MAIN PR

SUB Y/V

SUB PB/C

SUB PR

TP3601

TP3604

TP3605

TP3606

TP3602

TP3603

P3601-16

P3601-15

P3902-5

P3902-3

63

1

8

15

30

3

10

17

5

12

19

37

39

41

47

44

56

58

53

49

MAIN S-VIDEO-C

MAIN S-VIDEO-Y

/MAIN VIDEO

VIDEO

INPUT

SELECT

VIDEO

INPUT

SELECT

LOGIC

I2C SERIAL DATA

FROM

SYSTEM CONTROL

BLOCK DIAGRAM

FROM

SYSTEM CONTROL

BLOCK DIAGRAM

SUB VIDEO

SUB

S-VIDEO-Y

SUB

S-VIDEO-C

I2C SERIAL CLOCK

B

B

Q5001

B

Q5006

B

Q5010

B

Q5002

B

Q5003

B

B

Q5507

B

Q5508

B

Q5509

Q5510

B

P3901-1

P3901-3

P3901-5

P3901-7

P3901-9

P5501-1

P5501-3

P5501-5

P5501-7

P5501-9

R

RGB-IN 2

DVI-IN

G

B

H-SYNC

V-SYNC

JK3901

JK5801

34

33

LOGIC

JK3601

JK3602

JK3501

JK4801

JK3502

C

Y

COMPONENT

-Y3

COMPONENT

-PB3

COMPONENT

-PR3

COMPONENT

-Y4

COMPONENT

-PB4

COMPONENT

-PR4

JK3603

JK3604

R

RGB-IN 1

G

B

H-SYNC

V-SYNC

JK5501

VCC

42

SW +9V

IC5501 (SW)

Q5802

IC5803 (DVI DECODER)

IC5504 (A/D CONVERTER)

IC5502 (SYNC SEPARATION)

IC5802 (EEPROM)

21

19

15

22

14

H

L

R

G

B

H

L

H

L

H

L

H

L

16

RGB1(H)RGB2(L)

<FROM IC6003(22)>

VCC

20

14

16

18

5

7

9

57

59

61

48

50

52

67

66

74

75

2

3

46

44

43

P3601-13

P3601-11

P3601-10

P3403-18

P3403-16

P3403-15

P3403-13

P3403-11

P3403-10

38

36

35

1

7

3

9

5

11

24

23

12

13

54

57

56

48

43

A/D

CONVERTER

A/D H-SYNC

A/D CLOCK

H-SYNC

V-SYNC

I2C

CONTROL

TMDS

DECODER

ENCRYPTED

DATA (24 bit)

CONTROL

UUENCRYPTED

DATA (24 bit)

XOR

MASK

PANEL

INTERFACE

LOGIC

I2C SERIAL DATA 1

I2C SERIAL CLOCK 1

TP5501

TP5502

TP5504 TP5505

TP5503

RESET(L)

I2C SERIAL CLOCK

TMDS DATA0(+)

TMDS DATA0(-)

TMDS DATA1(+)

TMDS DATA1(-)

TMDS DATA2(+)

TMDS DATA2(-)

DDC CLOCK

DDC DATA

TMDS CLOCK(+)

TMDS CLOCK(-)

I2C SERIAL DATA

I2C SERIAL CLOCK

I2C SERIAL DATA

RESET(L) <FROM IC6003(73)>

CARD Y/PB/PR DATA(8BIT)

3D Y/C SEPARATION

NTSC DECODER

A/D

Y/PB/PR --RGB CONVERTER

SHARPNESS CONTROL

TINT CONTROL

COLOR CONTROL

BRIGHTNESS CONTROL

FROM SD/PC CARD

SIGNAL PROCESS

BLOCK DIAGRAM

70-77

A/D

CONVERTER

2-9

A/D

CONVERTER

SYNC

SEPARATION

12-19

R

R DATA(8BIT)

G DATA(8BIT)

B DATA(8BIT)

G

B

30-37

10-17

95

72

83

LPF

Q5007

B

Q5012,

Q5013

B

LPF

Q5008

B

Q5011

B

LPF

Q5015

B

Q5023

B

Q5027

B

Q5016

B

Q5017

B

LPF

Q5024

B

Q5029,

Q5030

B

LPF

Q5025

B

Q5028

B

LPF

A/D

A/D

14

136

8

4

67

66

31

30

49-58

22-31

36-45

6-13

153-160

123-127,140-144

120-122,128,129,

138,139,145-147

199-206

5.6M FIFO

MEMORY

20-27

90

91

85

86

80

81

93

94

6

5

100

3

1

DRIVE

Q5801

DRIVE

47

44

48

Y/V

R

Y/PB/PR

76MHz CLOCK

Y

PB/PR

G

B

PB/C

PR

31

VCC

+9V

47

VCC

1

VCC

+5V

R7011

MAIN TUNER

VIDEO LEVEL

TP7001

TP7101

VCC

8

+5V

+3.3V

VCC

1,13,19,22,35,41,

49,52,53,58,66

+3.45V

VCC

2,18,34,47,60,107,119,

132,149,166,181,185,

195,197,208,213,224

VCC

67,69,77,79,89,91,100

VCC

173,177,189,229,233

VCC

3,17,33,46,59,106,131,

151,170,183,193,211,

236,241,246,253

+3.3V

VCC

6,18,29,38

43,57,67,78

VCC

82,84,88,95,97

+5V

IC5801

+3.3V

REG.

+5V

23

IC5503

+3.3V

REG.

18

+5V

VCC

16

+5V

+3.3V

11,22,23,

69,78,79

VCC

26,27,34,35,

39,42,45,46,

51,52,59,62

VCC

CARD V-SYNC

CARD H-SYNC

+3.3V

IC5006

+2.5V

REG.

45

IC5003

+2.5V

REG.

31

IC5004

+2.5V

REG.

45

GCM2+

16

V-SYNC

162

H-SYNC

CLOCK

V-SYNC

H-SYNC

163

32

21

20