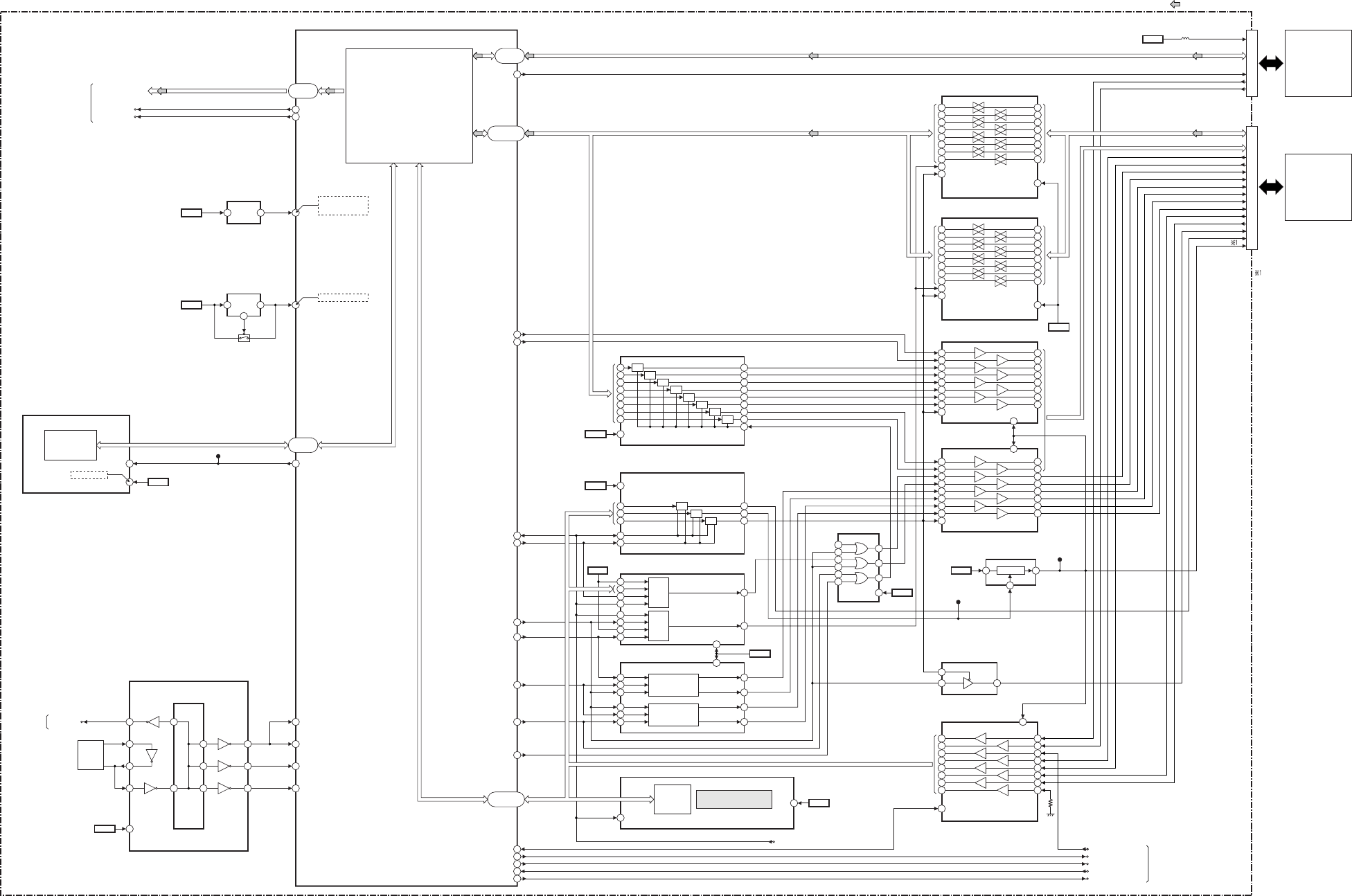

PT-50LC13

SD/PC CARD SIGNAL PROCESS BLOCK DIAGRAM

SD/PC CARD SIGNAL PROCESS BLOCK DIAGRAM

IC9004 (SD/PC CARD SIGNAL PROCESS)

IC9001 (128M SDRAM)

IC9003 (INVERTER)

IC9207 (TRANSCEIVER)

160-162,165

106-110,

113-115

77-82,85-90,

93-96

178-182,185-191,

194-197

122-128,131-137,

140,141

169

IC9208 (TRANSCEIVER)

IC9209 (BUFFER)

IC9211 (BUFFER)

2

3

4

5

6

7

8

9

1

19

1

19

19

19

18

17

16

15

14

13

12

11

IC9206 (OR GATE)

IC9204 (+5V REG.)

2

3

4

5

6

7

8

9

18

17

16

15

14

13

12

11

2

3

4

5

6

7

8

9

18

17

16

15

14

13

12

11

IC9210 (BUFFER)

18

17

16

15

14

13

12

11

2

3

4

5

6

7

8

9

18

17

16

15

14

13

12

11

IC9205 (D-FLIP/FLOP)

3

4

7

8

13

14

17

18

11

2

5

6

9

12

15

16

19

IC9201 (D-FLIP/FLOP)

11

13

14

1

9

10

12

15

F/F

F/F

F/F

IC9202 (D-FLIP/FLOP)

1

2

3

4

10

11

12

5

9

F/F

13

F/F

IC9203 (2 TO 4LINE DECODER)

1

2

3

13

14

15

4

5

11

12

2 TO 4LINE

DECODER

2 TO 4LINE

DECODER

F/F

F/F

F/F

F/F

F/F

F/F

F/F

DIRECTION

ENABLE

DIRECTION

ENABLE

ENABLE

ENABLE

F/F

154

155

118

119

128M SDRAM

SDRAM DATA (0-15)

CARD V-SYNC

CARD H-SYNC

CARD V-SYNC

SD/PC CARD

SIGNAL PROCESS

SD CLOCK

PC ADDRESS 0

PC ADDRESS 1

CARD RESET(L)

LCS1(L)

HCS3(L)

HRD

IO/MEM

HWR

HCS1(L)

CARD H-SYNC

CARD Y/PB/PR DATA

(0-7)

CARD Y/PB/PR DATA (8BIT) : 480i

TO VIDEO I

SIGNAL PATH

BLOCK DIAGRAM

IC9007 (FLASH MEMORY)

FLASH

MEMORY

SD CARD

PC CARD

SD WRITE PROTECT(L)

SD CARD DETECT(L)

PC CARD DETECT1(L)

PC CARD DETECT2(L)

CHIP ENABLE2

CHIP ENABLE1

OUTPUT ENABLE

I/O READ CONTROL

WRITE ENABLE

I/O WRITE CONTROL

VS1

VS2

REG

RESET(L)

+5V(PC CARD DETECTED)/0V(NO PC CARD)

SD CLOCK

P9002

P9201

SD DATA(0-3)

VCC(+3.3V)

L9012

SD DATA(0-3)

PC DATA(0-15)

DATA(0-15) DATA(0-7)

DATA(8-15)

PC DATA(0-15)

PC ADDRESS(0-9)

13

4

11

9

5 6

8

10

12

1

2

3

27MHz

OSC

27MHz CLOCK 27MHz CLOCK

27MHz CLOCK

27MHz CLOCK

27MHz CLOCK

TO VIDEO I

SIGNAL PATH

BLOCK DIAGRAM

X9001

116

117

105

49

MAIN C.B.A.

1

2

3

4

5

6

10

9

8

IC9212 (BUFFER)

2

1

4

174

24

153

150

149

152

CARD RESET(L) <FROM IC6003(43)>

+3.3V

+6.5V

158

+5V REG.

1

2

3

142

143

166

CARD SERIAL DATA 0

TO/FROM

SYSTEM CONTROL

BLOCK DIAGRAM

CARD SERIAL DATA 1

CARD SERIAL CLOCK

CARD CS(L)

CARD SERIAL DATA 1

CARD SERIAL CLOCK

CARD CS(L)

167

CARD READY(L)CARD READY(L)

175

LCS2(L)

2

3

4

5

6

7

8

9

IC9008

+3.5V

REG.

+2.8V

REG.

23

1,18,27,51,59,68,75,92,

99,104,111,130,148,157,

159,164,183,193,201

VCC

9,35,44,83,121,139,172

VCC

IC9002

32

4

+6.5V

+3.3V

Q9001

VCC

14

+3.3V

VCC

37

+3.3V

VCC

20

+3.3V

VCC

16

+3.3V

VCC

VCC

14

16

+3.3V

+3.3V

VCC

20

VCC

PC CARD ON(H)

14

+3.3V

RESET(L)

PROGRAM FOR

CARD PROCESSOR (IC9004)

12

ENABLE

19

1,3,9,14,27,43,49

VCC

94.5MHz94.5MHz

TP9001

VCC

VCC

20

20

VCC

20

VCC

20

+3.3V

+3.3V

CARD Y/PB/PR SIGNAL

102

38

TP9201

TP9202