KD-SH99R

1-40

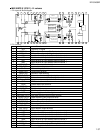

ANTI-

ALIASING

FILTER

CLOCKED

COMPARATOR

COSTAS LOOP

VARIABLE AND

FIXED DIVIDER

57 kHz

BANDPASS

(8th ORDER)

RECONSTRUCTION

FILTER

OSCILATOR

AND

DIVIDER

BIPHASE

SYMBOL

DECODER

TEST LOGIC AND OUTPUT

SELECTOR SWITCH

CLOCK

REGERATION

AND SYNC

REFERENCE

VOLTAGE

DIFFERENTIAL

DECODER

QUALITY BIT

GENERATOR

8

4

7

5

VP1

3

6 11

15

15

2

1

121413

910

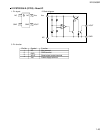

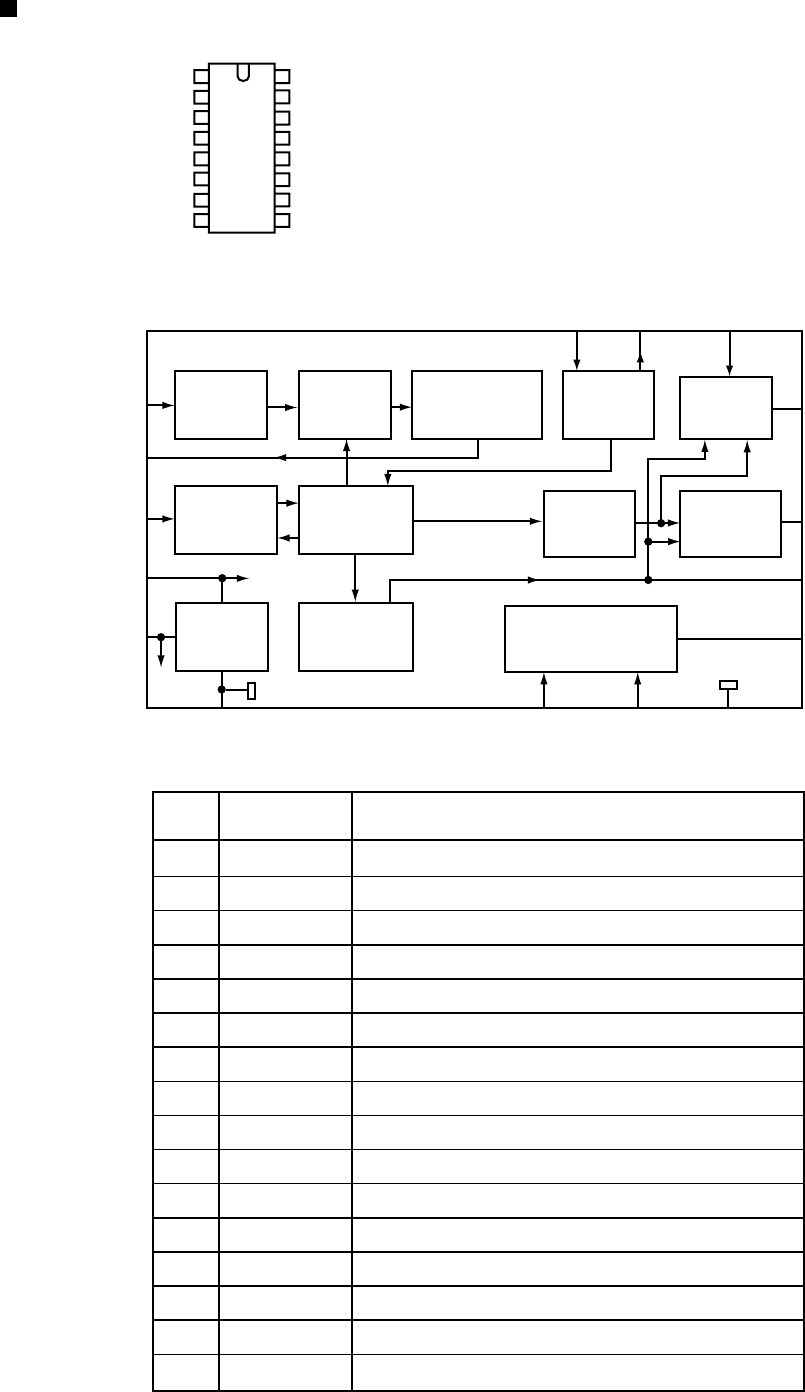

SAA6579T-X(IC51):RDS

1.Pin layout

2.Block diagram

3.Pin function

QUAL

RDDA

Vref

MUX

V

ODA

V

SSA

CIN

SCOUT

1

2

3

4

5

6

7

8

16

15

14

13

12

11

10

9

RDCL

T57

OSCO

OSCI

V

0DD

V

SSD

TEST

MODE

Symbol

QUAL

RDDA

Vref

MUX

VDDA

VSSA

CIN

SCOUT

MODE

TEST

VSSD

VDDD

OSCI

OSCO

T57

RDCL

Pin No.

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

Description

Quality indication output

RDS data output

Reference voltage output (0.5VDDA)

Multiolex signal input

+5V supply voltage for analog part

Ground for analog part (0V)

Subcarrier input to comparator

Subcarrier output of reconstruction filter

Oscllator mode / test control input

Test enable input

Ground for digital part (0V)

+5V supply voltage for digital part

Oscillator input

Oscillator output

57 kHz clock signal output

RDS clock output