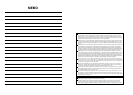

LC72151V LC72722/M/PMLC72151V LC72722/M/PM

CE DI CL DO I/O-1I/O-2 O-3

AOUT1

AV

SS

AREF

AIN1

AOUT2

AIN2

PDF

TGO

TGI2

TGI1

PDS

PDM2

PDS

PDM1

XBUF

XIN

XOUT

FMIN

AMIN

HCTR/I-3

LCTR/I-4

V

DD

V

SS

AV

DD

PHASE DETECTOR

CHARGE PUMP

UNLOCK

DETECTOR

CHARGE PUMP

for FAST LOCK

FAST LOCK UP

CONTROL

CCB

I/F

12bits PROGRAMMABLE

DIVIDER

SWALLOW COUNTER

1/16,1/17 4bits

REFERENCE

DIVIDER

UNIVERSAL

COUNTER

POWER

ON

RESET

DATA SHIFT REGISTER

LATCH

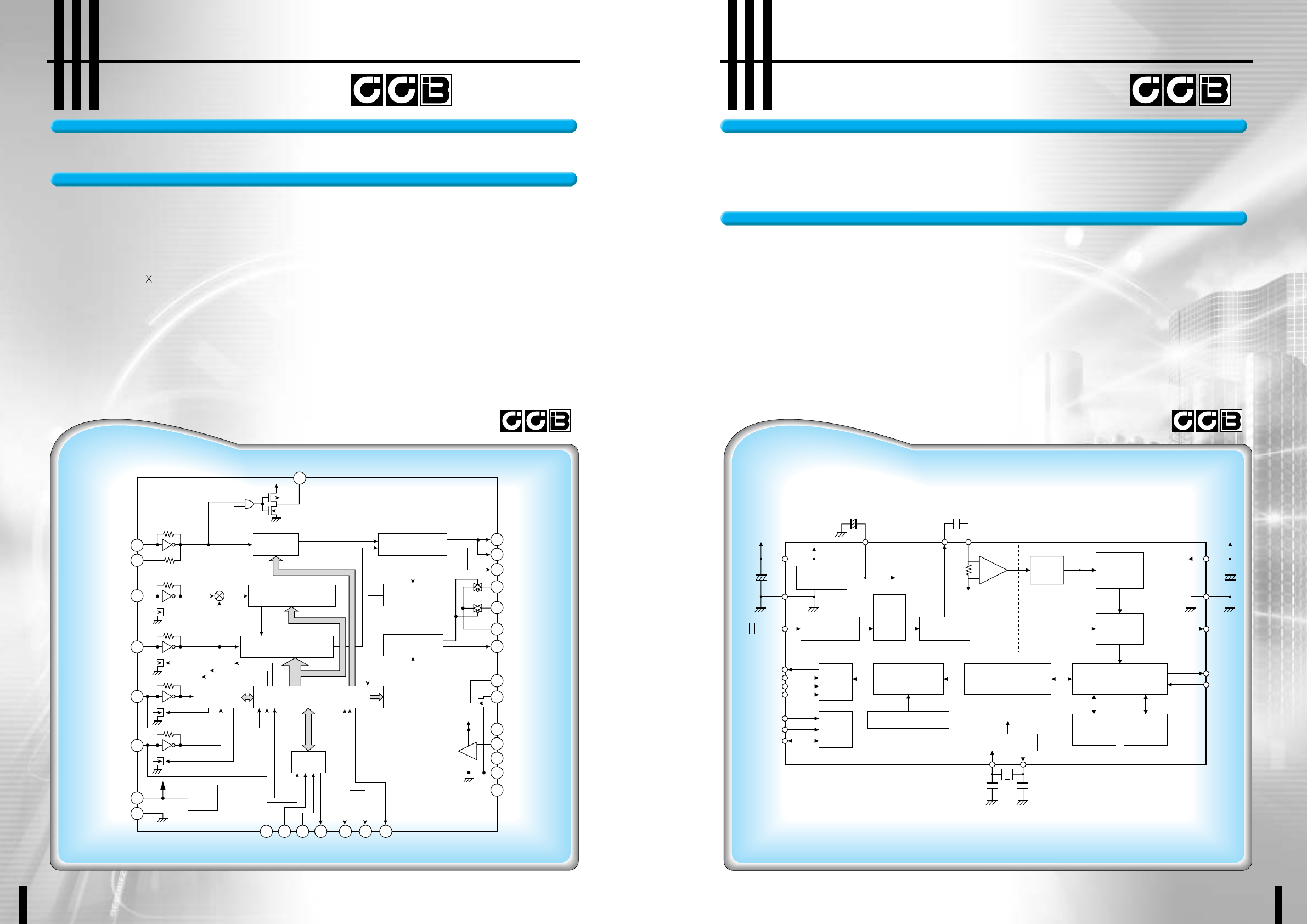

+

-

REFERENCE

VOLTAGE

ANTIALIASING

FILTER

SMOOTHING

FILTER

57kHz

BPF

(SCF)

TEST

PLL

(57kHz)

V

REF

CLOCK

RECOVERY

(1187.5Hz)

DATA

DECODER

SYNC

DETECT-2

SYNC

DETECT-1

OSC/DIVIDER

MEMORY CONTROL

CLK(4.332MHz)

+5V +5V

Vdda

Vssa

MPXIN

T2

T3 to T7

T1

CCB

DI

CE

CL

RAM

(24 BLOCK DATA)

ERROR CORRECTION

(SOFT DECISION)

SYNC/EC CONTROLLER

DO

X

IN

X

OUT

SYR

SYNC

RDS-ID

Vssd

Vddd

CINFLOUT

V

REF

+

-

69 Car Audio 70 Car Audio

Overview

Functions

Overview

Functions

Block Diagram Block Diagram

:CCB is SANYO's original bus format.

All bus addresses are managed by

SANYO for this format.

❋

❋

❋❋❋

:CCB is SANYO's original bus format.

All bus addresses are managed by

SANYO for this format.

❋

The LC72151V is a PLL frequency synthesizer IC that includes a high-speed locking circuit for FM reception.

This device makes it easy to implement high-performance RDS AM/FM tuners.

■ Bandpass filter: switched capacitor filter (SCF)

■ Demodulation: RDS data clock regeneration and demodulated data reliability information

■ Synchronization: Block synchronization detection with variable forward and backward

protection conditions

■ Error correction: soft decision and hard decision error correction

■ Buffer RAM: 24 blocks (about 500 ms) of data and flag memory

■ Data I/O: CCB interface (power on reset)

■ Packages:(LC72722):DIP24S(300mil)

(LC72722M):MFP24S(300mil)

(LC72722PM):MFP24(375mil)

RDS Signal-Processing System-on-Chip ICRDS Signal-Processing System-on-Chip IC

The LC72722, LC72722M, and LC72722PM are system-on-chip signal demodulation and processing ICs for

the European Broadcasting Union (EBU) Radio Data System (RDS) and the US National Radio System Committee

(NRSC) Radio Broadcast Data System (RBDS).

These ICs integrate, on the same chip, bandpass filter, demodulation, synchronization, and error correction

circuits as well as buffer RAM, and provide effective error correction using soft decision error correction.

■ High-speed programmable dividers

◆

FMIN: 10 to 160 MHz pulse swallower

◆

AMIN: 2 to 40 MHz pulse swallower

0.5 to 10 MHz direct divider

■ IF counters

◆

HCTR: 0.4 to 25 MHZ for FM IF counting

◆

LCTR: 10 to 500 kHz for AM IF counting

1.0 to 20 10

3

Hz for frequency

measurement

■ Reference frequency

◆

One of 11 frequencies can be selected

(crystal element: 10.25 or 10.35 MHz)

◆

1.3 , 3.125, 5, 6.25, 9 , 10, 12.5, 25, 30 , and 50 kHz

: These frequencies cannot be used when a 10.25

crystal element is used.

■ Phase comparator

◆

Supports dead zone control

◆

Unlocked state detection circuit

◆

Deadlock clear circuit

Car Audio Electronic Tuning PLL

Frequency Synthesizer

Car Audio Electronic Tuning PLL

Frequency Synthesizer

■ Active low-pass filter amplifier

◆

Built-in operational amplifier for FM high-speed

locking circuit

◆

Built-in MOS transistor for AM

■ Crystal oscillator output buffer

■ I/O ports: general-purpose I/O: 2 pins

◆

Input: 4 pins (maximum)

◆

Output: 3 pins (maximum)

■ Serial data I/O

◆

Control and communication using the CCB format

■ Operating ranges

◆

Supply voltage: 4.5 to 5.5 V (VDD)

7.5 to 9.5 V (AVDD)

◆

Operating temperature: -40 to +85°C

■ Package: SSOP30 (275 mil)