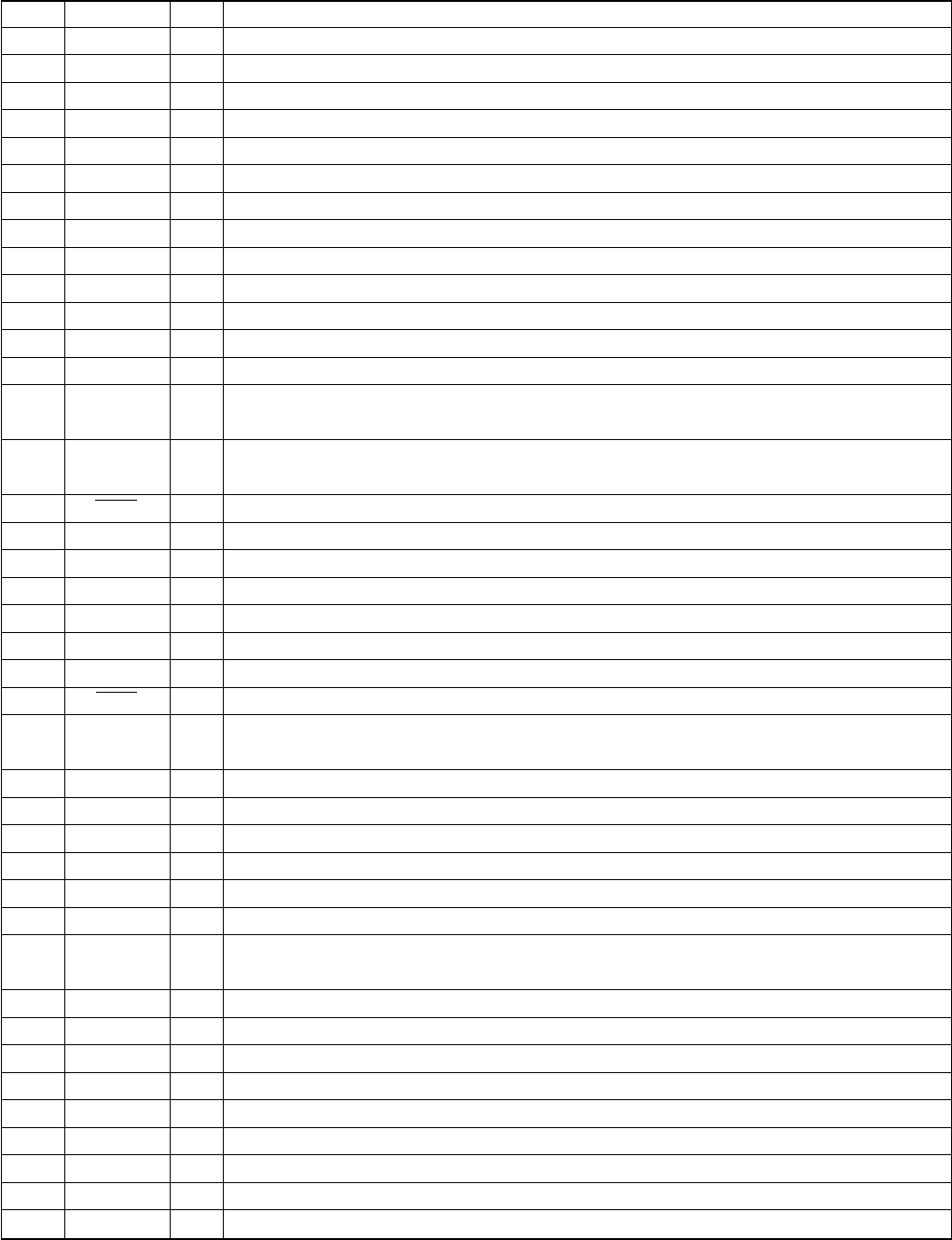

– 34 –

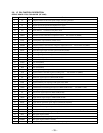

Pin No. Pin Name I/O Function

1 FS256 O 11.2896MHz clock signal output (MCLK system) Not used this set (OPEN)

2 FOK O Focus OK signal output to the system controller (IC600) “H” is output when the focus is applied

3 DFCT O Defect ON/OFF selection signal output to CXD2536CR (IC500)

4 SHCK O Track jump detection signal output to the system controller Not used this set (OPEN)

5 SHCKEN I Track jump detection enable input Not used this set (Fixed at “L”)

6 WRPWR I Laser power selection signal input from the system controller Not used this set (Fixed at “L”)

7 DIRC I Not used this set (Fixed at “H”)

8 SWDT I Write data signal input from the system controller (IC600)

9 SCLK I Serial clock signal input from the system controller (IC600)

10 XLAT I Serial latch signal input from the system controller (IC600)

11 SRDT O Read data signal output to the system controller (IC600)

12 SENS O (3) Internal status (SENS) output to the system controller (IC600)

13 ADSY O ADIP sync signal output Not used this set (OPEN)

14 SQSY O

Sub-code Q sync (SCOR) output to the system controller (IC600)

“L” every 13.3msec, Almost “H”

15 DQSY O

Digital in U-bit CD format sub-code Q sync (SCOR) output to the system controller (IC600)

“L” every 13.3msec, Almost “H”

16 XRST I Reset sigmal input from the system controller (IC600) When reset “L”

17 TEST4 I Test input terminal (Fixed at “L”)

18 CLVSCK O Not used this set (OPEN)

19 TEST5 I Test input terminal (Fixed at “L”)

20 DOUT O Output terminal of the digital audio signal (for optical out) Not used this set (OPEN)

21 DIN I Input terminal of the digital audio signal (for optical out) Not used this set (Fixed at “L”)

22 FMCK O FM modulation clock signal output of the ADIP Not used this set (OPEN)

23 ATER O ADIP CRC flag output When error “H” Not used this set (OPEN)

24 REC I

Record/playback selection signal input

When recording :“H”, when playback :“L” (Fixed at “L”)

25 DVSS – Ground terminal (Digital system)

26 DOVF I Validity flag input terminal for the digital audio out Not used this set (Fixed at “L”)

27 DODT I Input terminal of 16-bit data signal for the digital audio out Not used this set (Fixed at “L”)

28 DIDT O Output terminal of 16-bit data signal for the digital audio in Not used this set (OPEN)

29 DTI I Record audio data signal input from CXD2536CR (IC500)

30 DTO O (3) Plyback audio data signal output to CXD2536CR (IC500)

31 C2PO O

C2PO (indicate the error state of the data) signal output to CXD2536AR (IC500)

Playback : C2PO (“H”), Digital recording : D. In-Vflag, Analog recording : “L”

32 BCK O Bit clock (2.8224MHz) signal output to CXD2536CR (IC500) (MCLK system)

33 LRCK O L/R clock (44.1kHz) signal output to CXD2536CR (IC500) (MCLK system)

34 XTAO O System clock (512Fs=22.5792MHz) signal output Not used this set (OPEN)

35 XTAI I System clock (512Fs=22.5792MHz) signal input from CXD2536CR (IC500)

36 MCLK O MCLK clock (22.5792MHz) signal output Not used this set (OPEN)

37 XBCK O BCK (pin #™) inverted output Not used this set (OPEN)

38 DVDDO – Power supply terminal (+3.3V) (Digital system)

39 WDCK O WDCK clock (88.2kHz) signal output (MCLK system) Not used this set (OPEN)

40 RFCK O RFCK clock (7.35kHz) signal output (MCLK system) Not used this set (OPEN)

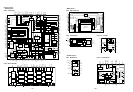

SERVO BOARD IC200 CDX2535CR-1 (DIGITAL SIGNAL PROCESSOR, DIGITAL SERVO SIGNAL PROCESSOR, EFM/ACIRC

ENCODER/DECODER)