SCD-XA5400ES

SCD-XA5400ES

1919

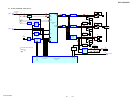

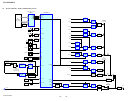

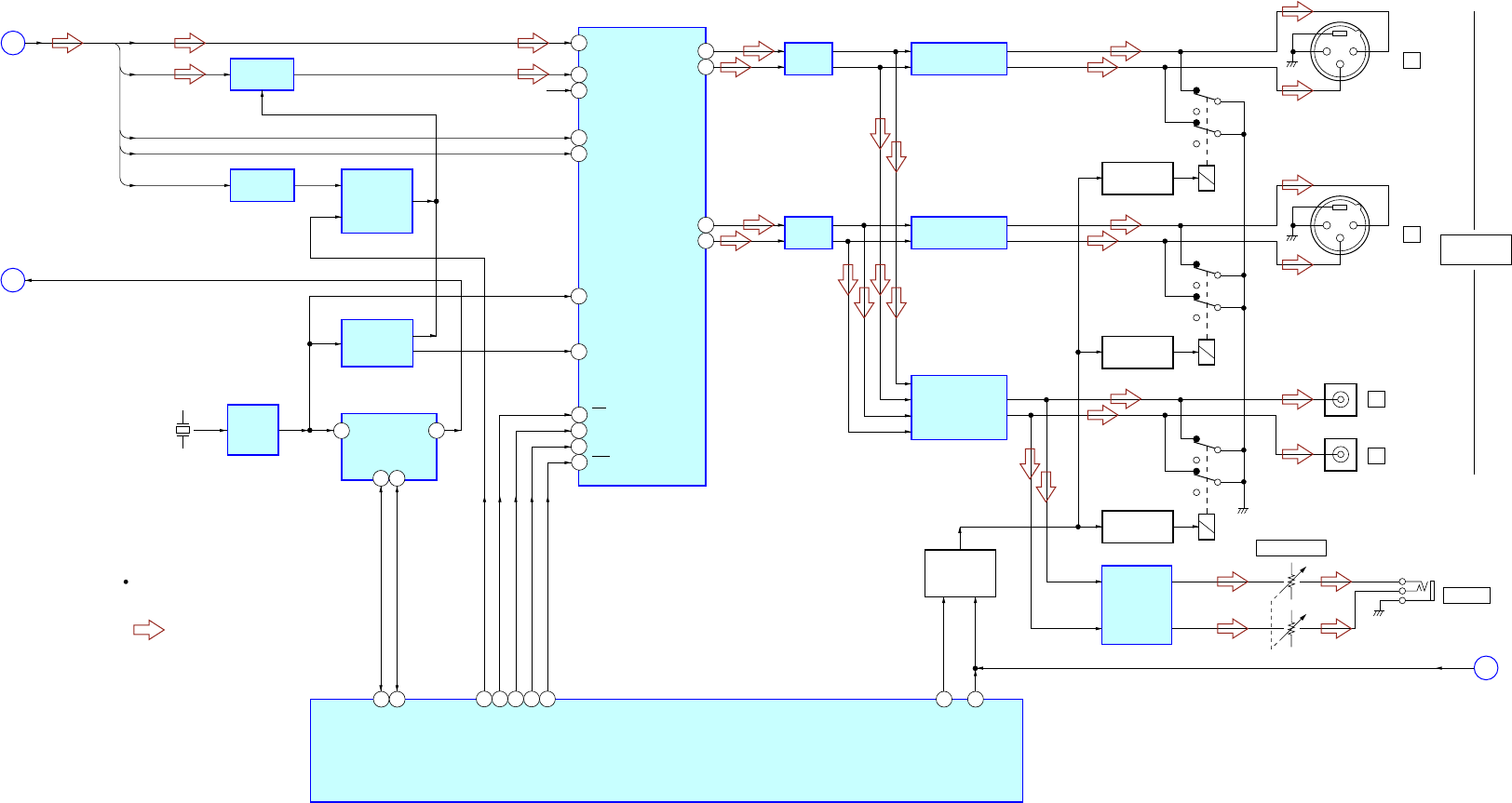

6-3. BLOCK DIAGRAM - MAIN Section -

• SIGNAL PATH

: SA-CD

A

B

BDTR

PBCK

PLRCK

PDT

PDT, BDTR, PBCK,

PLRCK, SBCK

27M

C

AC_DET

SWITCHING

IC206

SBCK

INVERTER

IC292

CLOCK

BUFFER

IC152

X151

22.5792MHz

D-FLIP FLOP

IC155

CLOCK GENERATOR

IC151

COUNTER

IC156

15CLKP

REF

2

PBCK

PLRCK

6

AB CK

3

SCK

7

RST

14

MS

10

PDATA

5

DSDL

1

DSDRR-CH

2

4

MDI

MDO

12

11

1

SCL

2

SDA

78

PLL_IC_ISC_SCL

77

PLL_IC_I2C_SDA

87

DAC_CS2

88

DAC_CS1

30

DAC_DATA

28

DAC_CLK

85

DAC_INT

6

XAMUTE

19

ASDMUTE

17IOUTR+

18IOUTR-

RY252

BUFFER

IC253

LOW-PASS FILTER

IC255

RELAY DRIVE

Q252, 253

1

2

4

3

4

J252

R

25IOUTL+

26IOUTL-

RY202

BUFFER

IC203

LOW-PASS FILTER

IC205

D/A CONVERTER

IC202

SYSTEM CONTROLLER

IC501 (3/4)

LINE AMP

IC291

BUFFER

IC204

RELAY DRIVE

Q202, 203

1

2

3

J202

L

PHONE LEVEL

ANALOG OUT

UNBALANCED

R

L

RY201

RV801

PHONES

J801

-1

-2

RELAY DRIVE

Q201, 204

RELAY

CONTROL

Q151, 293

J251

J201

R-ch is omitted due to same as L-ch.

(Page 17)

(Page 18)

(Page 20)