Physical Considerations

2-6

Evaluation Module Layout

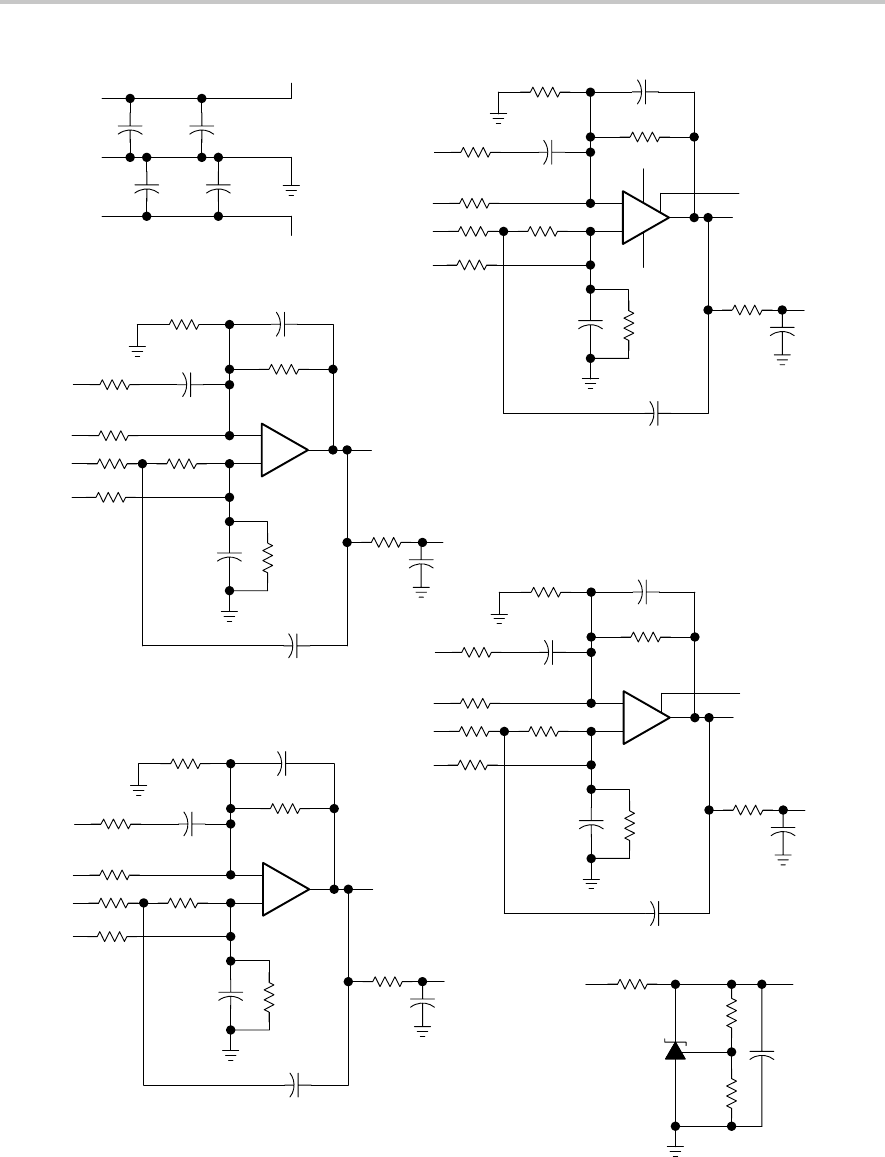

Figure 2–3. Area 300 Schematic—Quad Device SOIC (16 pin)

C313 C314

C311 C312

V3+

V3–

V3+

GND3

V3–

Power Supply Bypass

+

–

4

1

13

3

2

V3+

V3–

R302

C301

R304

C302

R301

R303

R305

R306

R308

R307

C304

C303

A3 OUT

A301–

A302–

A303+

A304+

U301A

C305

R309

A3 FLT

AB3/SD

8

+

–

7

5

6

R318

C308

R314

C310

R310

R312

R317

R313

R315

R311

C307

C309

B3 OUT

B301–

B302–

B303+

B304+

U301B

C306

R316

B3 FLT

+

–

10

12

11

R325

C316

R323

C317

R322

R324

R326

R327

R329

R328

C318

C319

C3 OUT

C301–

C302–

C303+

C304+

U301C

C320

R330

CD3/SD

9

+

–

16

14

15

R339

C321

R331

C324

R332

R333

R334

R335

R336

R337

C322

C325

D3 OUT

D301–

D302–

D303+

D304+

U301D

C323

R338

C3 FLT

D3 FLT

R320

U302

R319

Voltage Reference

V1+ VREF3

R321

C315