3 - 28

3. SIGNALS AND WIRING

3.7 Interfaces

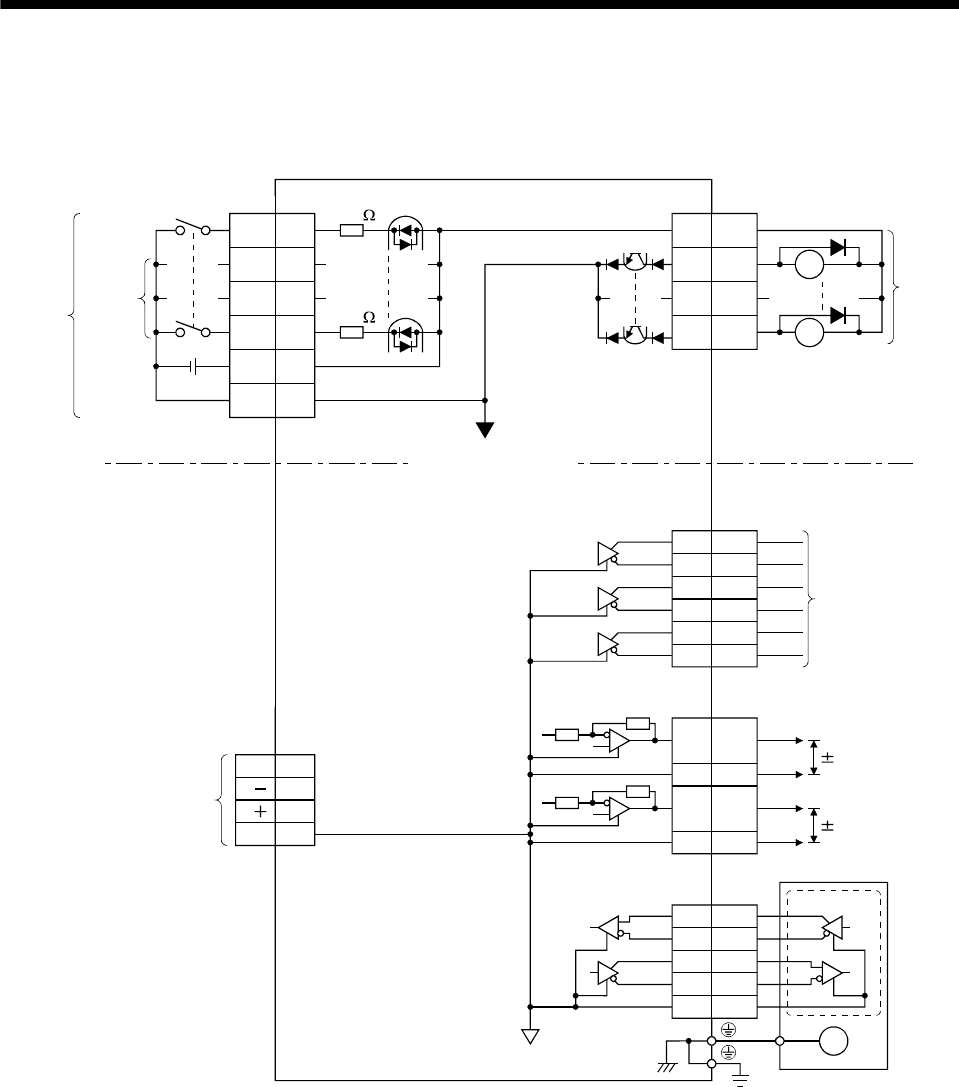

3.7.1 Internal connection diagram

3

EM1

CN3

20

DI1 2

DI2 12

DI3 19

DICOM

5

3

CN3

10

13

9

15

DICOM

(Note 2)

INP

ALM

CN3

6

16

7

17

8

18

LA

LAR

LB

LBR

LZ

LZR

RA

CN3

MO1

MO2

LG

4

14

11

RA

Differential line

driver output

(35mA or less)

<Isolated>

Approx

5.6k

Analog monitor

Servo amplifier

2

4

7

8

MR

MRR

MD

MDR

LG

Encoder

E

Servo motor

(Note 1)

USB

M

D

GND

VBUS

D

1

2

3

5

CN5

LG1

MBR

DOCOM

24VDC

Forced stop

CN2

(Note 3)

(Note 3)

Approx

5.6k

10VDC

10VDC

Note 1. Signal can be assigned for these pins with host controller setting.

For contents of signals, refer to the instruction manual of host controller.

2. This signal cannot be used with speed loop mode.

3. For the sink I/O interface. For the source I/O interface, refer to section 3.7.3.