HDI08 – DSP-Side Programmer’s Model

DSP56366 24-Bit Digital Signal Processor User Manual, Rev. 4

6-12 Freescale Semiconductor

6.5.5.2 HBAR Reserved Bits 8-15

These bits are reserved. They read as zero and should be written with zero for future compatibility.

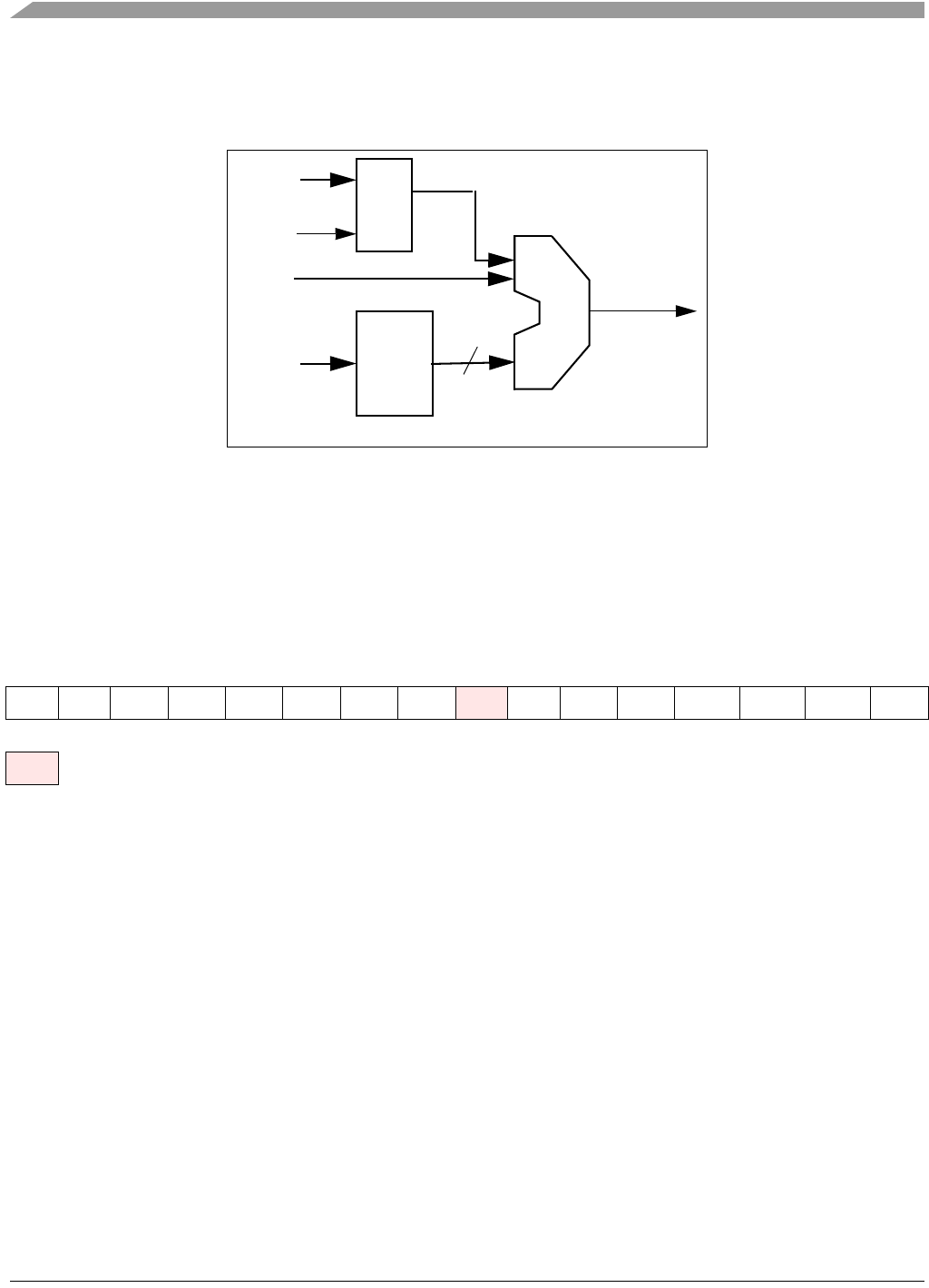

Figure 6-5 Self Chip Select logic

6.5.6 Host Port Control Register (HPCR)

The HPCR is a 16-bit read/write control register used by the DSP to control the HDI08 operating mode.

The initialization values for the HPCR bits are described in Section 6.5.9, "DSP-Side Registers After

Reset". The HPCR bits are described in the following paragraphs.

NOTE

To assure proper operation of the HDI08, the HPCR bits HAP, HRP, HCSP,

HDDS, HMUX, HASP, HDSP, HROD, HAEN and HREN should be

changed only if HEN is cleared. Also, the HPCR bits HAP, HRP, HCSP,

HDDS, HMUX, HASP, HDSP, HROD, HAEN, HREN, HCSEN, HA9EN

and HA8EN should not be set when HEN is set or simultaneously with

setting HEN.

6.5.6.1 HPCR Host GPIO Port Enable (HGEN) Bit 0

If the HGEN bit is set, pins configured as GPIO are enabled. If this bit is cleared, pins configured as GPIO

are disconnected: outputs are high impedance, inputs are electrically disconnected. Pins configured as

HDI08 are not affected by the state of HGEN.

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

HAP HRP HCSP HDDS HMUX HASP HDSP HROD HEN HAEN HREN HCSEN HA9EN HA8EN HGEN

- Reserved bit. Read as 0. Should be written with 0, for future compatibility.

Figure 6-6 Host Port Control Register (HPCR) (X:$FFFFC4)

Latch

HAD[0-7]

Chip select

COMPARATOR

A[3:7]

8 bits

HAS

HA[8:10]

DSP Peripheral

data bus

Base

Address

register

BA[3:7]