Serial Host Interface Programming Model

DSP56366 24-Bit Digital Signal Processor User Manual, Rev. 4

Freescale Semiconductor 7-3

user’s responsibility to select the proper clock rate within the range as defined in the I

2

C and SPI bus

specifications.

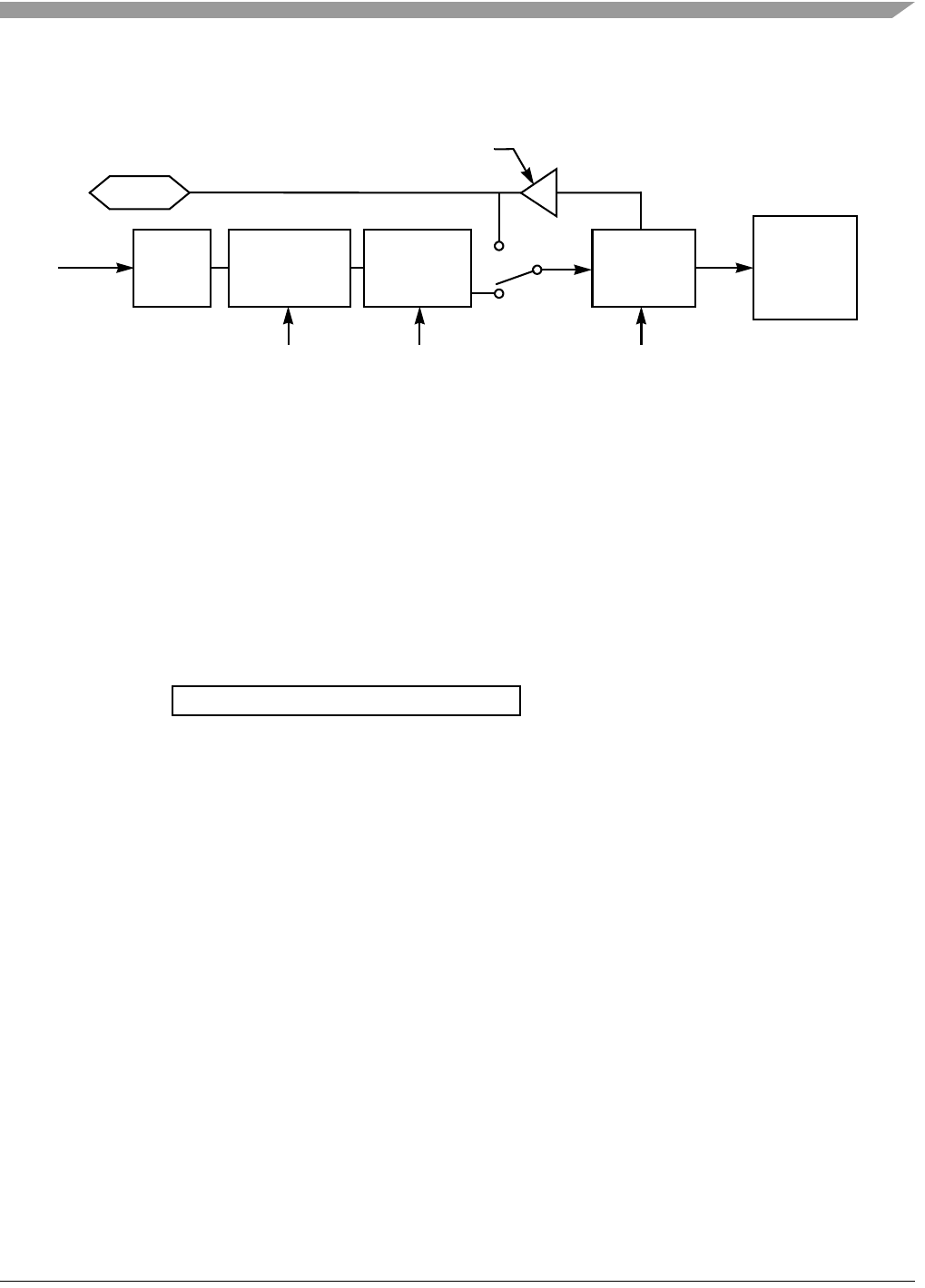

Figure 7-2 SHI Clock Generator

7.4 Serial Host Interface Programming Model

The Serial Host Interface programming model has two parts:

• Host side—see Figure 7-3 below and Section 7.4.1, "SHI Input/Output Shift Register

(IOSR)—Host Side"

• DSP side—see Figure 7-4 and Section 7.4.2, "SHI Host Transmit Data Register (HTX)—DSP

Side" through Section 7.4.6, "SHI Control/Status Register (HCSR)—DSP Side" for detailed

information.

Figure 7-3 SHI Programming Model—Host Side

SHI

HMST

HMST = 0

HMST = 1

SCK/SCL

Divide By

1 or 8

Divide By 1

To

Divide By 256

HRSHDM0–HDM7

SHI Clock

F

OSC

Divide

By 2 Controller

Clock

Logic

CPHA, CPOL, HI

2

C

AA0417

0

I/O Shift Register (IOSR)

IOSR

23

AA0418