Serial Host Interface

DSP56366 24-Bit Digital Signal Processor User Manual, Rev. 4

2-12 Freescale Semiconductor

2.8 Serial Host Interface

The SHI has five I/O signals that can be configured to allow the SHI to operate in either SPI or I

2

C mode.

HACK/

HACK

Input GPIO

disconnected

Host Acknowledge — When HDI08 is programmed to interface a single

host request host bus and the HI function is selected, this signal is the host

acknowledge (HACK) Schmitt-trigger input. The polarity of the host

acknowledge is programmable, but is configured as active-low (HACK

) after

reset.

HRRQ/

HRRQ

Output Receive Host Request — When HDI08 is programmed to interface a

double host request host bus and the HI function is selected, this signal is

the receive host request (HRRQ) output. The polarity of the host request is

programmable, but is configured as active-low (HRRQ

) after reset. The host

request may be programmed as a driven or open-drain output.

PB15 Input, output, or

disconnected

Port B 15 — When the HDI08 is configured as GPIO, this signal is

individually programmed as input, output, or internally disconnected.

The default state after reset for this signal is GPIO disconnected.

This input is 5 V tolerant.

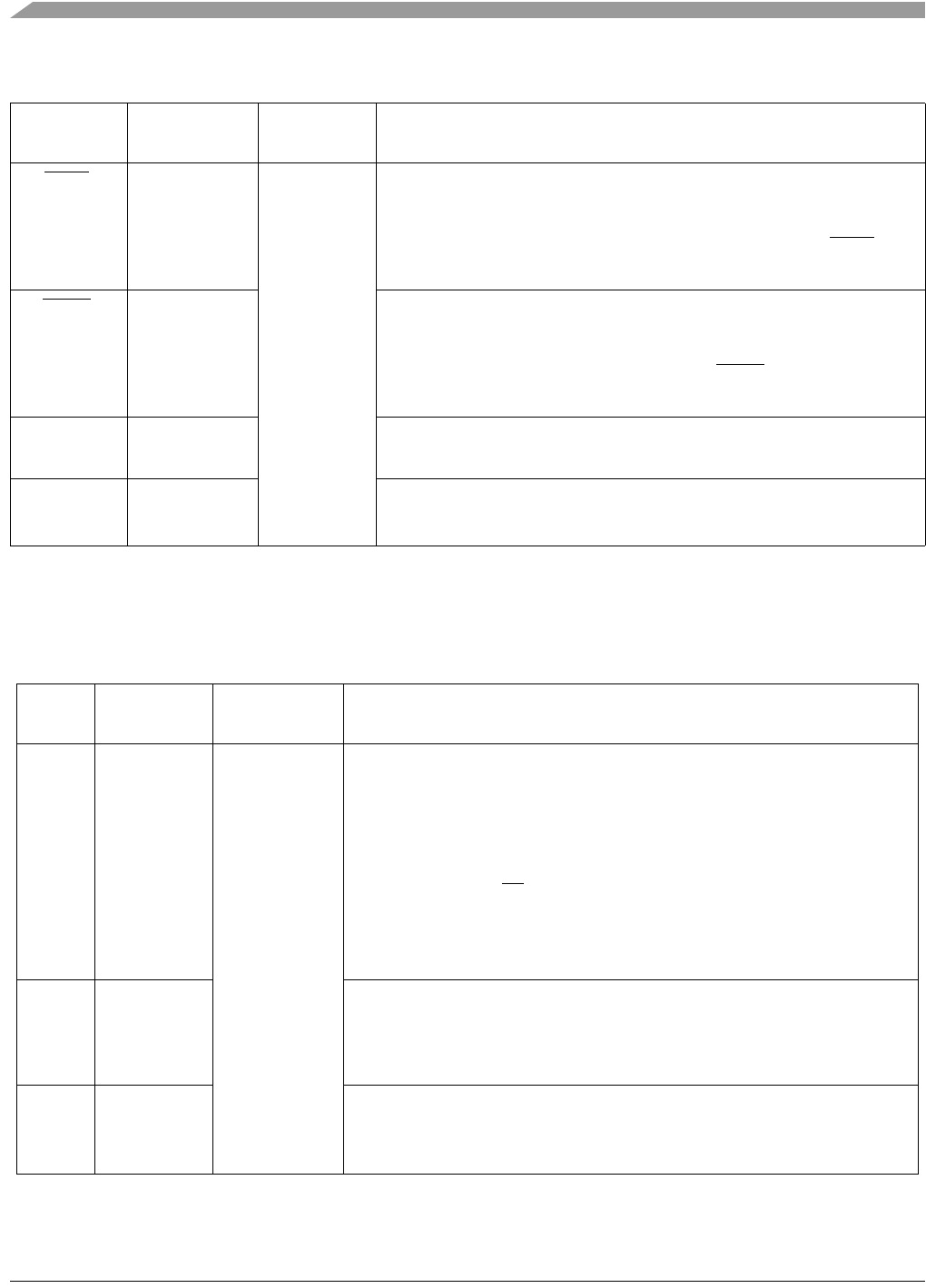

Table 2-10 Serial Host Interface Signals

Signal

Name

Signal Type

State during

Reset

Signal Description

SCK Input or output Tri-stated SPI Serial Clock — The SCK signal is an output when the SPI is configured as

a master and a Schmitt-trigger input when the SPI is configured as a slave.

When the SPI is configured as a master, the SCK signal is derived from the

internal SHI clock generator. When the SPI is configured as a slave, the SCK

signal is an input, and the clock signal from the external master synchronizes

the data transfer. The SCK signal is ignored by the SPI if it is defined as a slave

and the slave select (SS

) signal is not asserted. In both the master and slave

SPI devices, data is shifted on one edge of the SCK signal and is sampled on

the opposite edge where data is stable. Edge polarity is determined by the SPI

transfer protocol.

SCL Input or output I

2

C Serial Clock — SCL carries the clock for I

2

C bus transactions in the I

2

C

mode. SCL is a Schmitt-trigger input when configured as a slave and an

open-drain output when configured as a master. SCL should be connected to

V

CC

through a pull-up resistor.

This signal is tri-stated during hardware, software, and individual reset. Thus,

there is no need for an external pull-up in this state.

This input is 5 V tolerant.

Table 2-9 Host Interface (continued)

Signal Name Type

State during

Reset

Signal Description