HDI08 – External Host Programmer’s Model

DSP56366 24-Bit Digital Signal Processor User Manual, Rev. 4

Freescale Semiconductor 6-27

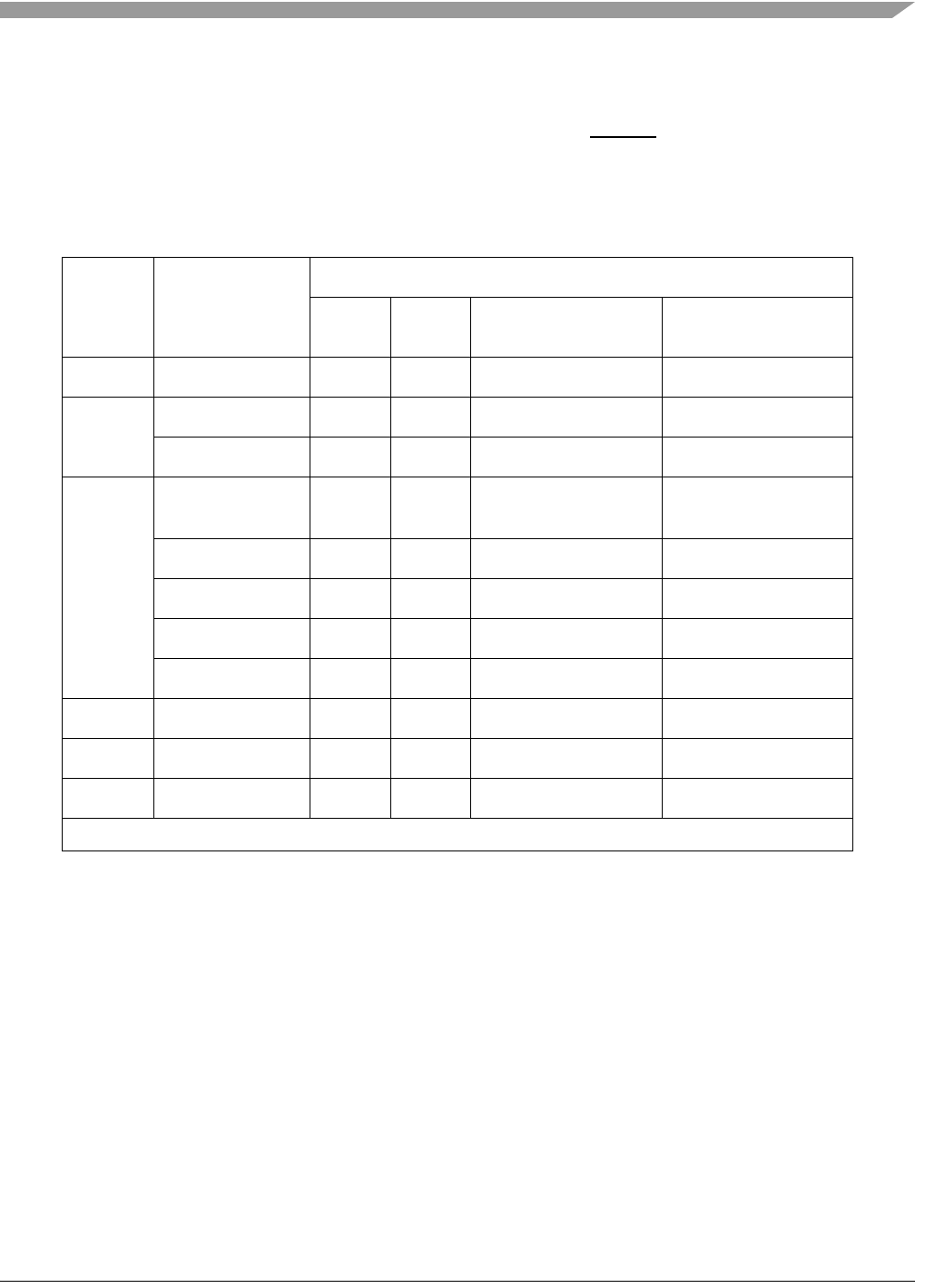

6.6.7 Host Side Registers After Reset

Table 6-15 shows the result of the four kinds of reset on bits in each of the HDI08 registers seen by the

host processor. The hardware reset (HW) is caused by asserting the RESET signal. The software reset

(SW) is caused by executing the RESET instruction. The individual reset (IR) is caused by clearing the

HEN bit in the HPCR register. The stop reset (ST) is caused by executing the STOP instruction.

6.6.8 General Purpose INPUT/OUTPUT (GPIO)

When configured as general-purpose I/O, the HDI08 is viewed by the DSP core as memory-mapped

registers (see Section 6.5, "HDI08 – DSP-Side Programmer’s Model") that control up to 16 I/O pins. The

software and hardware resets clear all DSP-side control registers and configure the HDI08 as GPIO with

all 16 signals disconnected. External circuitry connected to the HDI08 may need external

pull-up/pull-down resistors until the signals are configured for operation. The registers cleared are the

HPCR, HDDR and HDR. Selection between GPIO and HDI08 is made by clearing HPCR bits 6 through

1 for GPIO or setting these bits for HDI08 functionality. If the HDI08 is in GPIO mode, the HDDR

configures each corresponding signal in the HDR as an input signal if the HDDR bit is cleared or as an

output signal if the HDDR bit is set (see Section 6.5.7, "Data direction register (HDDR)" and

Section 6.5.8, "Host Data Register (HDR)").

Table 6-15 Host Side Registers After Reset

Register

Name

Register

Data

Reset Type

HW

Reset

SW

Reset

IR

Reset

ST

Reset

ICR All Bits 0 0 — —

CVR HC 0 0 0 0

HV[6:0] $32 $32 — —

ISR HREQ 0 0 1 if TREQ is set;

0 otherwise

1 if TREQ is set;

0 otherwise

HF3-HF2 0 0 — —

TRDY 1 1 1 1

TXDE 1 1 1 1

RXDF 0 0 0 0

IVR IV[7:0] $0F $0F — —

RX RXH:RXM:RXL empty empty empty empty

TX TXH:TXM:TXL empty empty empty empty

Note: A long dash (—) denotes that the register value is not affected by the specified reset.