Programming Sheets

DSP56366 24-Bit Digital Signal Processor User Manual, Rev. 4

D-18 Freescale Semiconductor

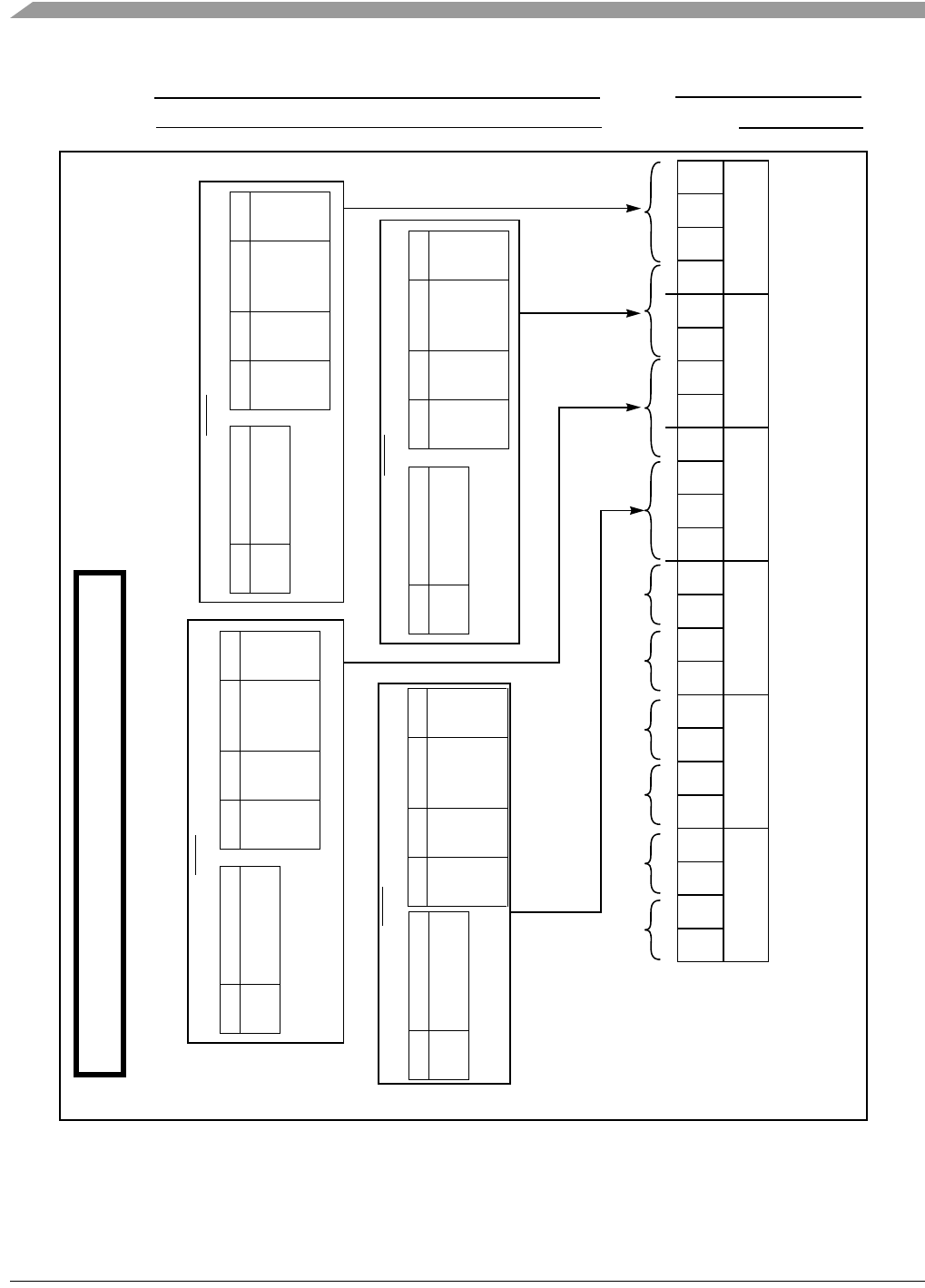

Figure D-3. Interrupt Priority Register–Core (IPR–C)

Application:

Date:

Programmer:

Sheet 3 of 5

CENTRAL PROCESSOR

15 14 13 12 11 10

9

876543210

D1L0 IDL2 IDL1 IBL2 IBL1 IBL0 IAL2 IAL1 IAL0

Interrupt Priority

X:$FFFFFF R/W

D0L1D0L0

Reset = $000000

Register (IPR–C)

23 22 21 20 19 18 1617

D1L1

IAL2 Trigger

0 Level

1 Neg. Edge

IRQA Mode

IAL1 IAL0 Enabled IPL

00 No—

01Yes0

10Yes1

11Yes2

IBL2 Trigger

0 Level

1 Neg. Edge

IRQB Mode

IBL1 IBL0 Enabled IPL

00 No—

01Yes0

10Yes1

11Yes2

ICL0ICL1ICL2

IDL0

D2L0D2L1D3L0D3L1D4L0

D4L1

D5L0D5L1

ICL2 Trigger

0 Level

1 Neg. Edge

IRQC Mode

ICL1 ICL0 Enabled IPL

00 No—

01Yes0

10Yes1

11Yes2

IDL2 Trigger

0 Level

1 Neg. Edge

IRQD Mode

IDL1 IDL0 Enabled IPL

00 No—

01Yes0

10Yes1

11Yes2