DAX Programming Considerations

DSP56366 24-Bit Digital Signal Processor User Manual, Rev. 4

Freescale Semiconductor 10-11

non-audio data bits of the next frame are stored in XNADR and one frame of audio data to be transmitted

in the next frame is stored in the FIFO by two consecutive MOVEP instructions to XADR. If the non-audio

bits are not changed from frame to frame, this procedure can be handled within a fast interrupt routine.

Storing the next frame’s audio data in the FIFO clears the XADE bit in the XSTR.

10.6.3 Block Transferred Interrupt Handling

An interrupt with the XBLK vector indicates the end of a block transmission and may require some

computation to provide the next non-audio data structures that are to be transmitted within the next block.

Within the routine, the next audio data can be stored in the FIFO by two consecutive MOVEP instructions

to XADR, and the next non-audio data can be stored in the XNADR. The XBLK interrupt occurs only if

the XBIE bit in XCTR is set. If XBIE is cleared, a XADE interrupt vector will take place.

10.6.4 DAX operation with DMA

During DMA transfers, the XDIE bit of the XCTR must be cleared to avoid XADE interrupt services by

the DSP core. The initialization appearing in Section 10.6.1, "Initiating A Transmit Session" is relevant

for DMA operation. DMA transfers can be performed with or without changing non-audio bits from frame

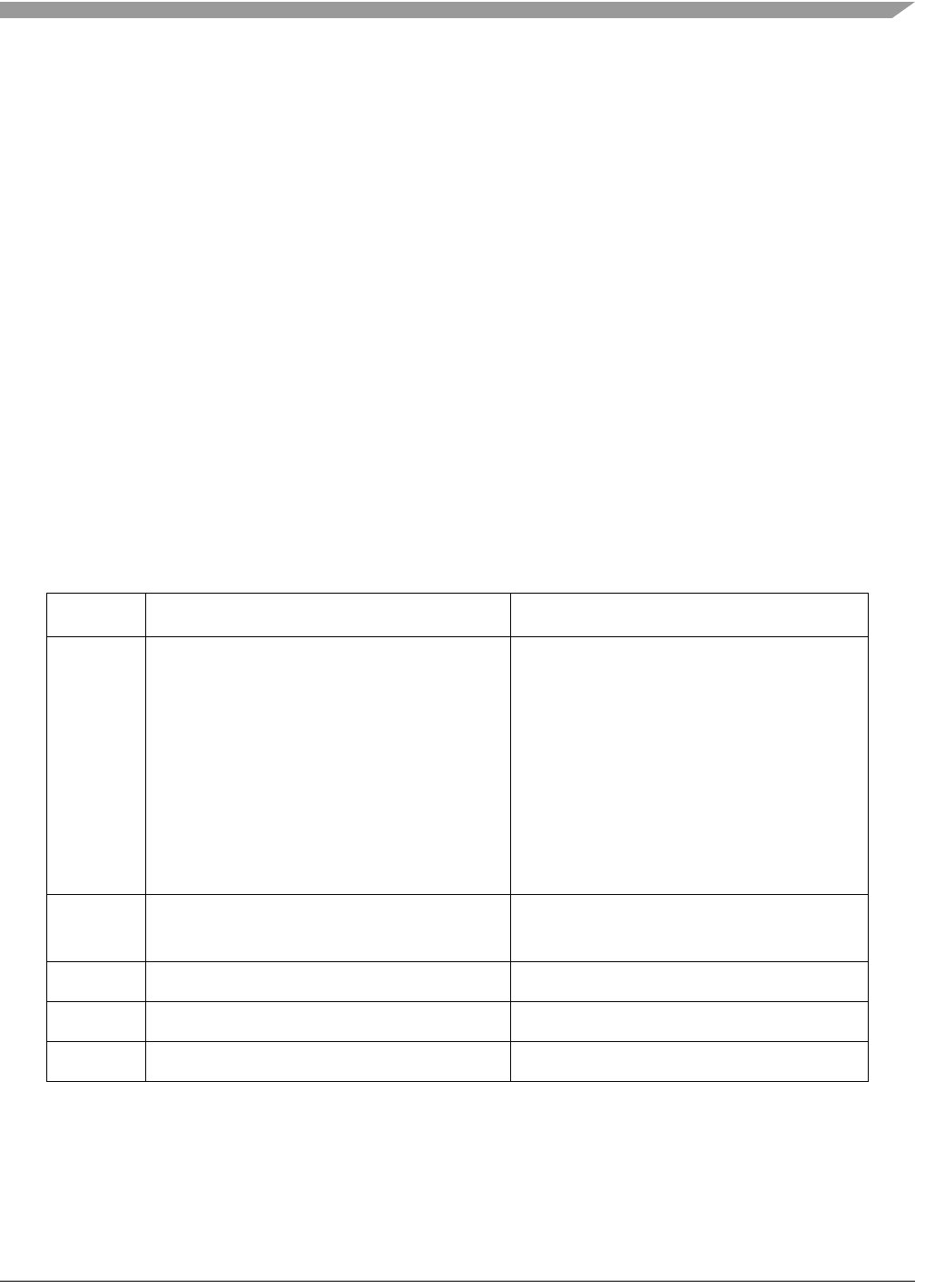

to frame. Table 10-5 describes two examples of DMA configuration.

The memory organization employed for DMA transfers depends on whether or not non-audio data changes

from frame to frame as shown in Figure 10-6.

Table 10-5 Examples of DMA configuration

Register Non-audio data bits change Non-audio data bits do not change

DCR2 DE=1; Enable DMA channel.

DIE=1; Enable DMA interrupt.

DTM[2:0]=010; Line transfer mode.

D3D=0; Not 3D.

DAM[5:3]=000; 2D mode.

DAM[2:0]=101; post increment by 1.

DDS[1:0]=00; X memory space.

DRS[4:0]=01010; DAX is DMA request source.

Other bits are application dependent.

DE=1; Enable DMA channel.

DIE=1; Enable DMA interrupt.

DTM[2:0]=010; Line transfer mode.

D3D=0; Not 3D.

DAM[5:3]=000; 2D mode.

DAM[2:0]=101; post increment by 1.

DDS[1:0]=00; X memory space.

DRS[4:0]=01010; DAX is DMA request source.

Other bits are application dependent.

DCO2 DCOH=number of frames in block - 1

DCOL=$002; 3 destination registers

DCOH=number of frames in block - 1

DCOL=$001; 2 destination registers

DSR2 first memory address of the block first memory address of the block

DDR2 XNADR address (base address + $1) XADR address (base address + $2)

DOR0 $FFFFFE; offset=-2 $FFFFFF; offset=-1