Programming Sheets

DSP56366 24-Bit Digital Signal Processor User Manual, Rev. 4

Freescale Semiconductor D-37

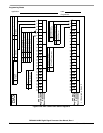

Figure D-22. ESAI_1 Transmit Clock Control Register

Application:

Date:

Programmer:

15 6 5 419 18 17 16 10 9 8 714 13 12 11

TPM0

3210

TPM2

23 22 21 20

TPM1

TPM3TPM4TPM5TPM6TPM7TPSRTDC0TDC1TDC2TDC3TDC4TFP0TFP1TFP2TFP3TCKPTFSPTHCKPTCKDTFSDTHCKD

TCKP Description

0

1

Transmitter Clock Polarity set to clockout on rising edge of

transmit clock, latch in on falling edge of transmit clock.

Transmitter Clock Polarity set to clockout on falling edge of

TFSP Description

0

1

Frame sync polarity positive

Frame sync polarity negative

TFP [3:0]

Description

Divider control.

TCKD

Description

0

1

External clock source used

Internal clock source

TFSD Description

0

1

FST_1 is input

FST_1 is output

THCKD Description

0

1

Reserved

Must be set for proper operation

THCKP Description

0

1

Keep cleared for proper operation

Reserved

Range $0 - $F (1 -16).

TDC [4:0] Description

Divider control. Range $00 - $FF (1 - 32)

TPM [7:0] Description

Specifies the prescaler divide rate is

transmitter clock generator

TPSR Description

0

1

Divide by 8 prescaler operational

Divide by 8 prescaler bypassed

Range from $00 - $FF (1 - 256).

AA1777

for the

ESAI_1

TCCR_1 - ESAI_1 Transmit Clock Control Register

Y: $FFFF96 Reset: $000000

transmit clock, latch in on rising edge of transmit clock