Timer/Event Counter Programming Model

DSP56366 24-Bit Digital Signal Processor User Manual, Rev. 4

11-6 Freescale Semiconductor

11.3.2.3 TPLR Reserved Bit 23

This reserved bit is read as zero and should be written with zero for future compatibility.

11.3.3 Timer Prescaler Count Register (TPCR)

The TPCR is a 24-bit read-only register that reflects the current value in the prescaler counter. See

Figure 11-5.

11.3.3.1 TPCR Prescaler Counter Value PC[20:0] Bits 20–0

These 21 bits contain the current value of the prescaler counter.

11.3.3.2 TPCR Reserved Bits 23–21

These reserved bits are read as zero and should be written with zero for future compatibility.

11.3.4 Timer Control/Status Register (TCSR)

The TCSR is a 24-bit read/write register controlling the timer and reflecting its status.

11.3.4.1 TCSR Timer Enable (TE) Bit 0

The timer enable (TE) bit is used to enable or disable the timer. Setting TE enables the timer and clears the

timer counter. The counter starts counting according to the mode selected by the timer control (TC[3:0])

bit values.

Table 11-1 Prescaler Source Selection

PS1 PS0 PRESCALER CLOCK SOURCE

0 0 Internal CLK/2

01 TIO0

10 Reserved

11 Reserved

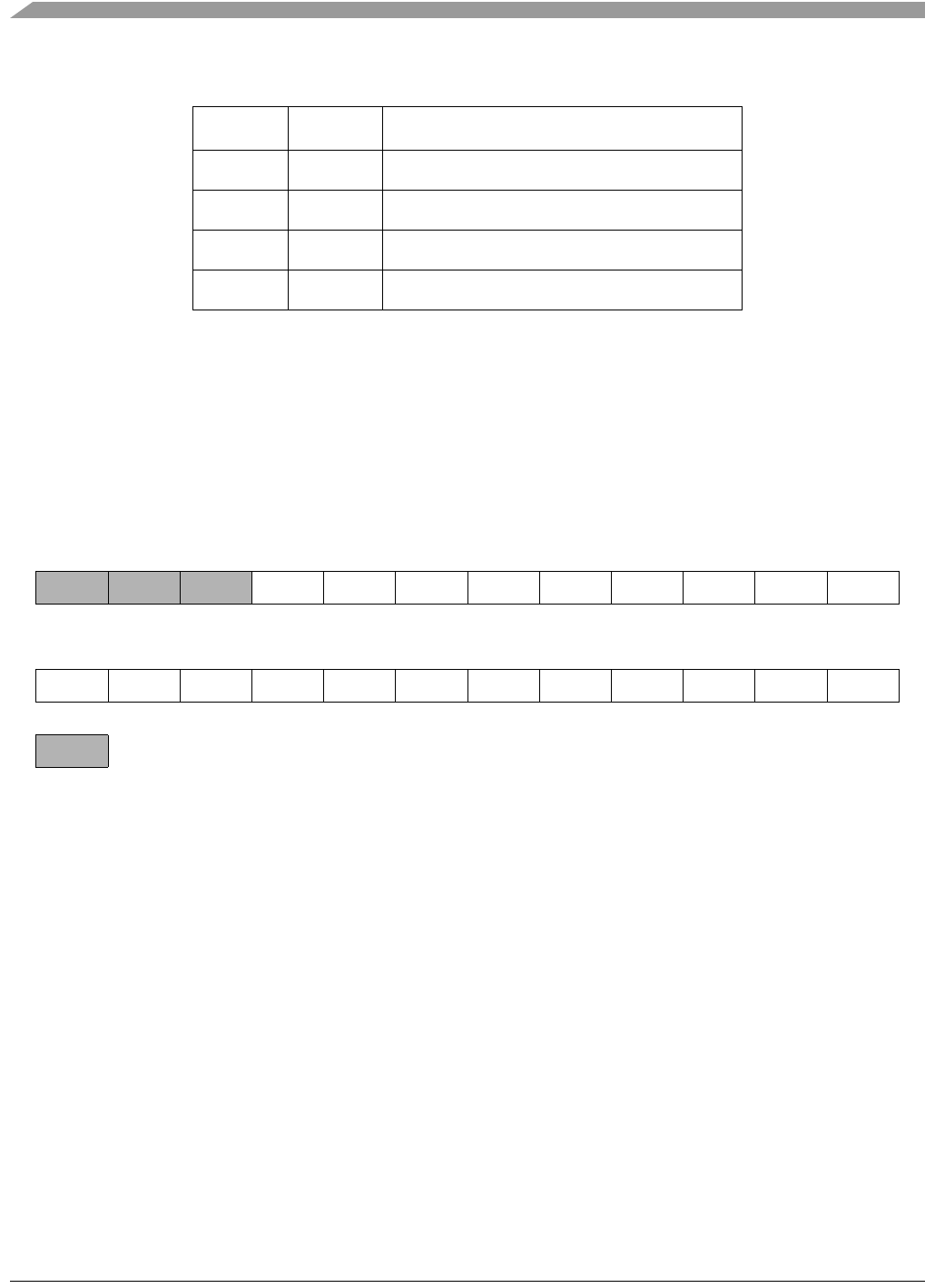

23 22 21

20 19 18 17 16 15 14 13 12

PC20 PC19 PC18 PC17 PC16 PC15 PC14 PC13 PC12

11109876543210

PC11 PC10 PC9 PC8 PC7 PC6 PC5 PC4 PC3 PC2 PC1 PC0

— reserved, read as 0, should be written with 0 for future compatibility

Figure 11-5 Time Prescaler Count Register (TPCR)