Serial Host Interface Programming Model

DSP56366 24-Bit Digital Signal Processor User Manual, Rev. 4

7-6 Freescale Semiconductor

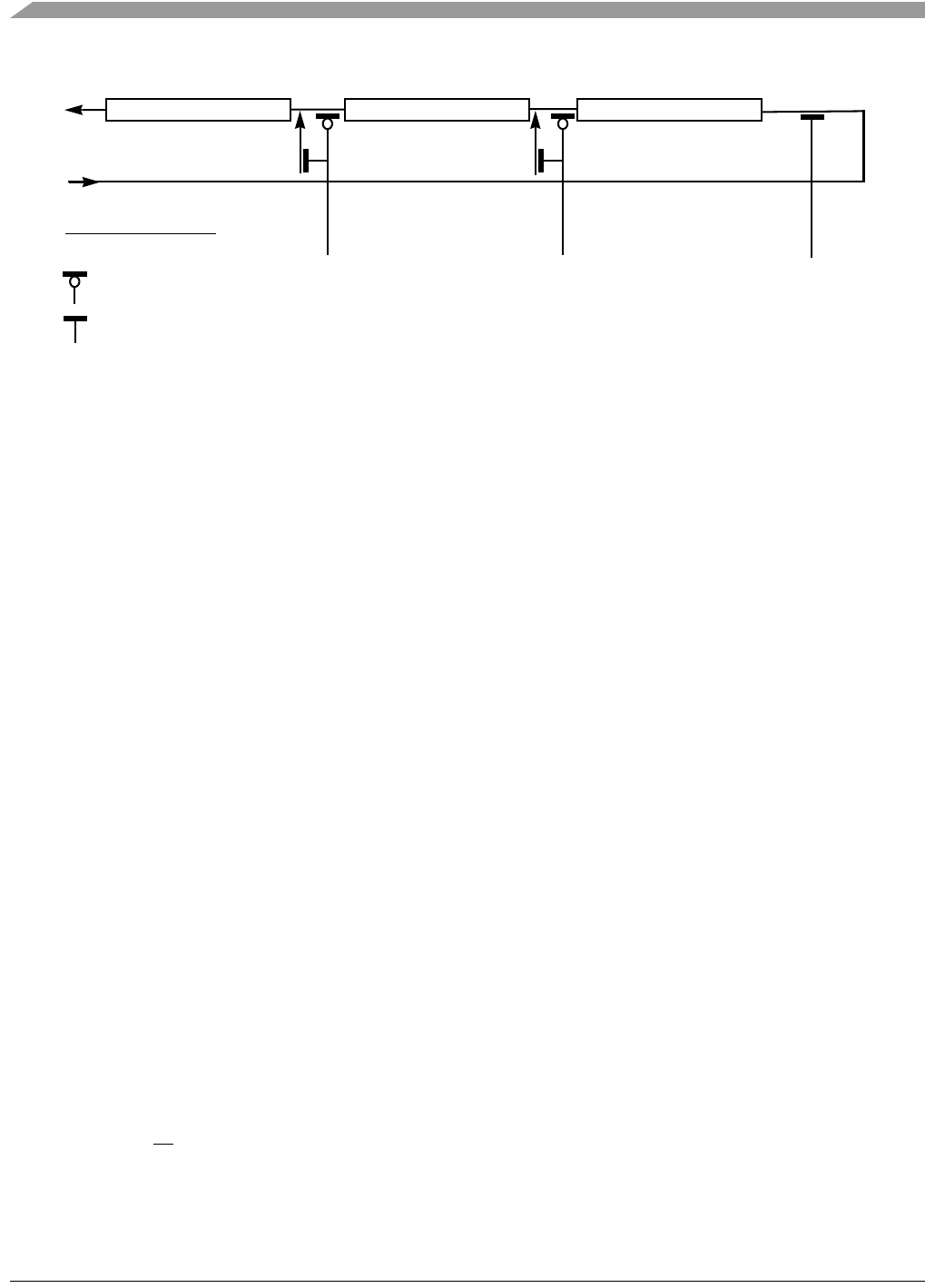

Figure 7-5 SHI I/O Shift Register (IOSR)

7.4.2 SHI Host Transmit Data Register (HTX)—DSP Side

The host transmit data register (HTX) is used for DSP-to-Host data transfers. The HTX register is 24 bits

wide. Writing to the HTX register by DSP core instructions or by DMA transfers clears the HTDE flag.

The DSP may program the HTIE bit to cause a host transmit data interrupt when HTDE is set (see

Section 7.4.6.10, "HCSR Transmit-Interrupt Enable (HTIE)—Bit 11"). Data should not be written to the

HTX until HTDE is set in order to prevent overwriting the previous data. HTX is reset to the empty state

when in stop mode and during hardware reset, software reset, and individual reset.

In the 8-bit data transfer mode the most significant byte of the HTX is transmitted; in the 16-bit mode the

two most significant bytes, and in the 24-bit mode all the contents of HTX is transferred.

7.4.3 SHI Host Receive Data FIFO (HRX)—DSP Side

The 24-bit host receive data FIFO (HRX) is a 10-word deep, First-In-First-Out (FIFO) register used for

Host-to-DSP data transfers. The serial data is received via the shift register and then loaded into the HRX.

In the 8-bit data transfer mode, the most significant byte of the shift register is transferred to the HRX (the

other bits are cleared); in the 16-bit mode the two most significant bytes are transferred (the least

significant byte is cleared), and in the 24-bit mode, all 24 bits are transferred to the HRX. The HRX may

be read by the DSP while the FIFO is being loaded from the shift register. Reading all data from HRX

clears the HRNE flag. The HRX may be read by DSP core instructions or by DMA transfers. The HRX

FIFO is reset to the empty state when the chip is in stop mode, and during hardware reset, software reset,

and individual reset.

7.4.4 SHI Slave Address Register (HSAR)—DSP Side

The 24-bit slave address register (HSAR) is used when the SHI operates in the I

2

C slave mode and is

ignored in the other operational modes. HSAR holds five bits of the 7-bit slave device address. The SHI

also acknowledges the general call address specified by the I

2

C protocol (eight zeroes comprising a 7-bit

address and a R/W

bit), but treats any following data bytes as regular data. That is, the SHI does not

differentiate between its dedicated address and the general call address. HSAR cannot be accessed by the

host processor.

16

23

8

15

0

7

8-Bit Data

Mode

16-Bit Data

Mode

24-Bit Data

Mode

Mode of Operation

Stops Data When Data Mode is Selected

Passes Data When Data Mode is Selected

AA0420