DAX Internal Architecture

DSP56366 24-Bit Digital Signal Processor User Manual, Rev. 4

Freescale Semiconductor 10-9

10.5.8 DAX Parity Generator (PRTYG)

The PRTYG generates the parity bit for the subframe being transmitted. The generated parity bit ensures

that subframe bits four to thirty-one will carry an even number of ones and zeroes.

10.5.9 DAX Biphase Encoder

The DAX biphase encoder encodes each audio and non-audio bit into its biphase mark format and shifts

this encoded data out to the ADO output pin synchronously to the biphase clock.

10.5.10 DAX Preamble Generator

The DAX preamble generator automatically generates one of three preambles in the 8-bit preamble shift

register at the beginning of each subframe transmission, and shifts it out. The generated preambles always

start with “0”. Bit patterns of preambles generated in the preamble generator are shown in Table 10-4. The

preamble bits are already in the biphase mark format.

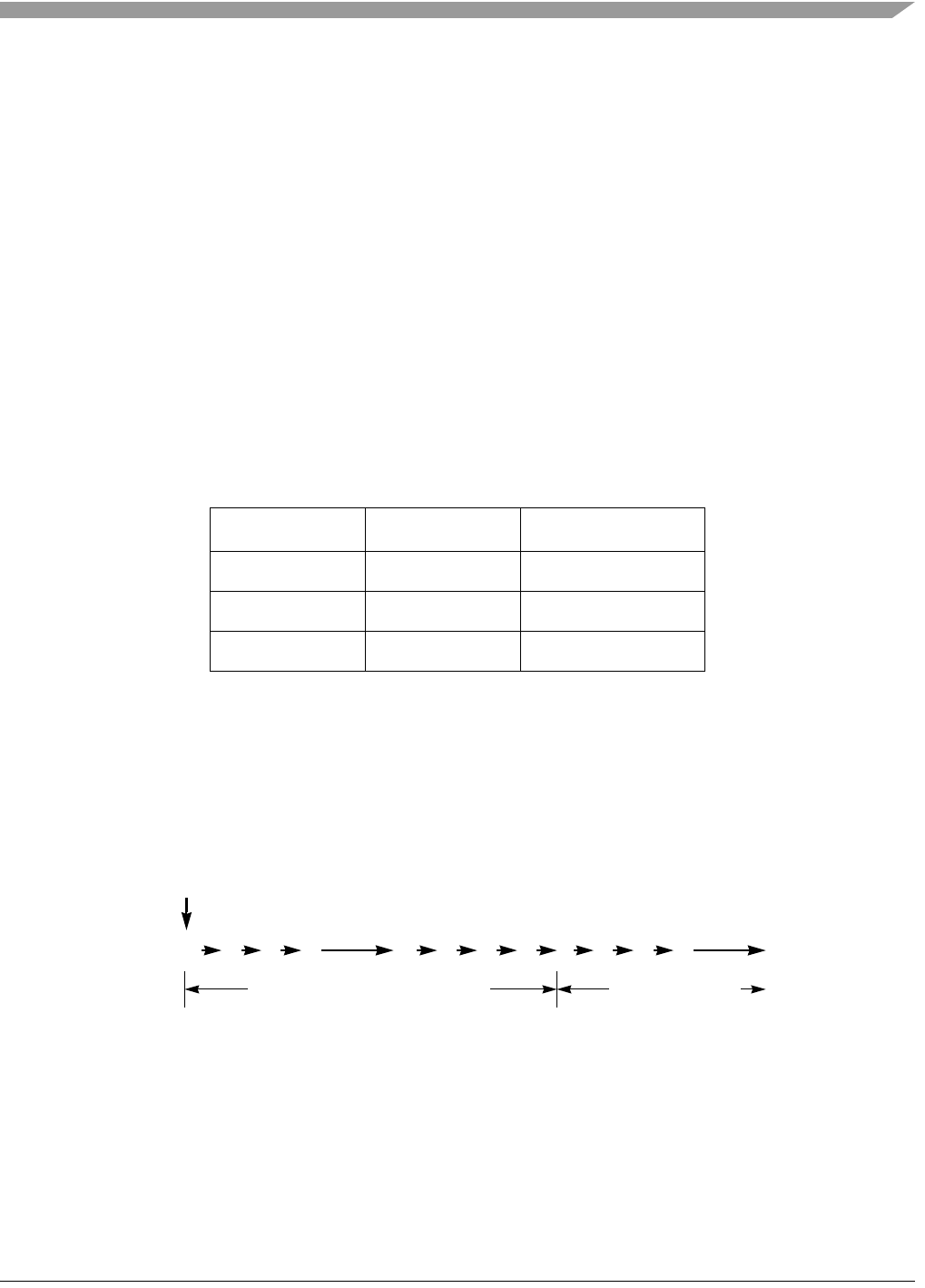

There is no programmable control for the preamble selection. The first subframe to be transmitted

(immediately after the DAX is enabled) is the beginning of a block, and therefore it has a “Z” preamble.

This is followed by the second subframe, which has an “Y” preamble. After that, “X” and “Y” preambles

are transmitted alternately until the end of the block transfer (192 frames transmitted). See Figure 10-4 for

an illustration of the preamble sequence.

Figure 10-4 Preamble sequence

10.5.11 DAX Clock Multiplexer

The DAX clock multiplexer selects one of the clock sources and generates the biphase clock (128 × Fs)

and shift clock (64 × Fs). The clock source can be selected from the following options (see also

Section 10.5.6.4, "DAX Clock Input Select (XCS[1:0])—Bits 3–4").

Table 10-4 Preamble Bit Patterns

Preamble Bit Pattern Channel

X 00011101 A

Y 00011011 B

Z 00010111 A (first in block)

DAX

Enabled

Here

First Block (384 subframes) Second Block

Z Y X Y X Y X Y Z Y X Y

AA0609k