DAX Internal Architecture

DSP56366 24-Bit Digital Signal Processor User Manual, Rev. 4

10-8 Freescale Semiconductor

10.5.7.1 DAX Audio Data Register Empty (XADE)—Bit 0

The XADE status flag indicates that the DAX audio data register XADR and the audio data buffer

XADBUFA are empty (and ready to receive the next frame’s audio data). This bit is set at the beginning

of every frame transmission (more precisely, when channel A audio data is transferred from XADBUFA

to XADSR). When XADE is set and the interrupt is enabled (XDIE = 1), an audio data register empty

interrupt request is sent to the DSP core. XADE is cleared by writing two channels of audio data to XADR.

10.5.7.2 DAX Transmit Underrun Error Flag (XAUR)—Bit 1

The XAUR status flag is set when the DAX audio data buffers XADBUFA or XADBUFB are empty and

the respective audio data upload occurs. When a DAX underrun error occurs, the previous frame data will

be retransmitted in both channels. When XAUR is set and the interrupt is enabled (XUIE = 1), an underrun

error interrupt request is sent to the DSP core. This allows programmers to write an exception handling

routine for this special case. The XAUR bit is cleared by reading the XSTR register with XAUR set,

followed by writing two channels of audio data to XADR.

10.5.7.3 DAX Block Transfer Flag (XBLK)—Bit 2

The XBLK flag indicates that the frame being transmitted is the last frame in a block. This bit is set at the

beginning of the transmission of the last frame (the 191st frame). This bit does not cause any interrupt.

However, if XBIE=1 it causes a change in the interrupt vector sent to DSP core in the event of an audio

data register empty interrupt, so that a different interrupt routine can be called (providing the next

non-audio data structures for the next block as well as storing audio data for the next frame). Writing two

channels of audio data to XADR clears this bit.

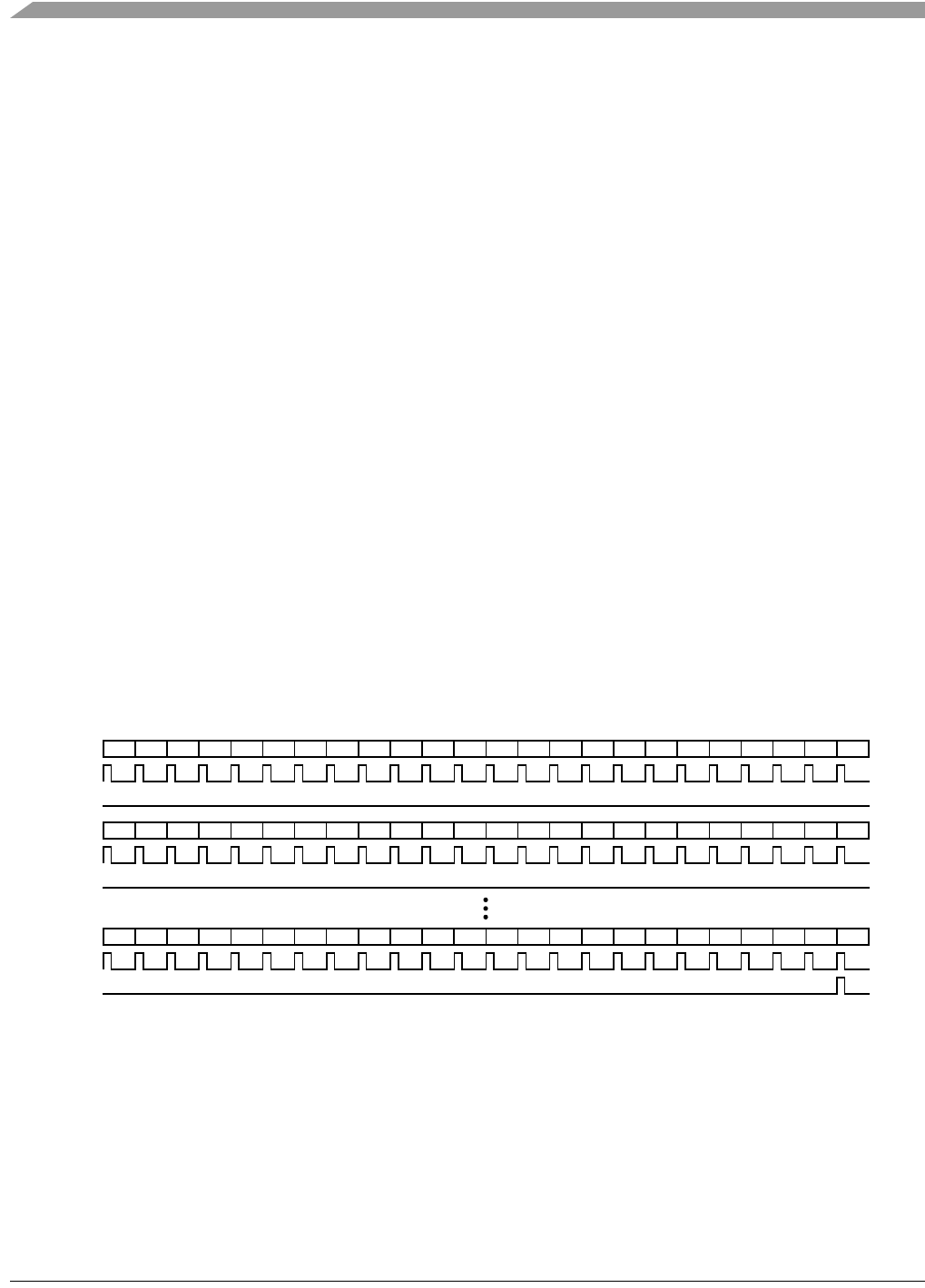

The relative timing of transmit frames and XADE and XBLK flags is shown in Figure 10-3.

Figure 10-3 DAX Relative Timing

10.5.7.4 XSTR Reserved Bits—Bits 3–23

These XSTR bits are reserved. They read as 0, and should be written with 0 to ensure compatibility with

future device versions.

#000 #001 #008#007#006#005#004#003#002 #009 #010 #021#011 #018#017#016#015#014#013#012 #019 #020 #022 #023

#024 #025 #032#031#030#029#028#027#026 #033 #034 #045#035 #042#041#040#039#038#037#036 #043 #044 #046 #047

XADE

XBLK

Frame

XADE

XBLK

Frame

XADE

XBLK

Frame

#168 #169 #176#175#174#173#172#171#170 #177 #178 #189#179 #186#185#184#183#182#181#180 #187 #188 #190 #191

AA0608