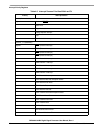

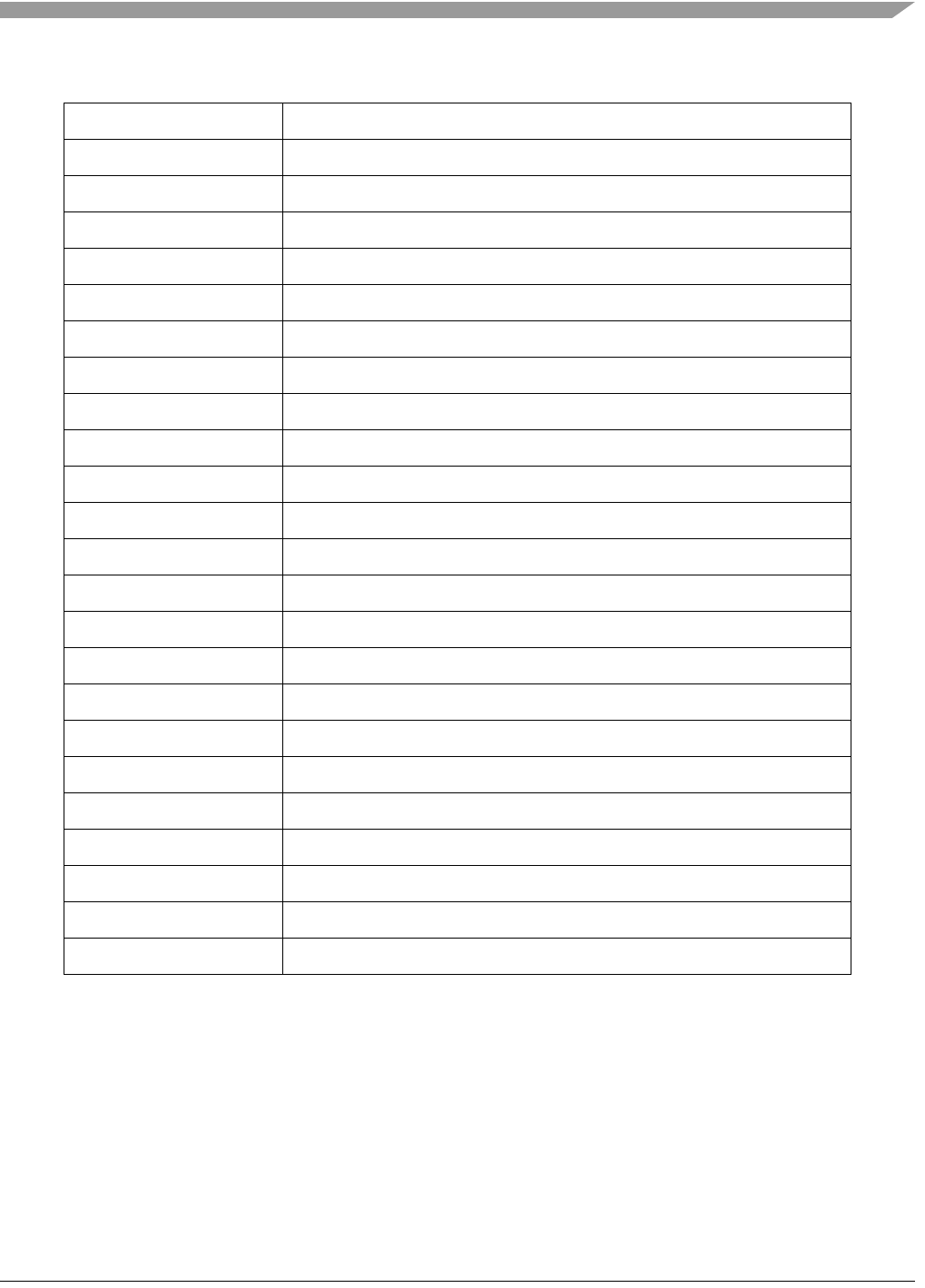

Interrupt Priority Registers

DSP56366 24-Bit Digital Signal Processor User Manual, Rev. 4

Freescale Semiconductor 4-9

SHI Receive FIFO Full

SHI Transmit Data

SHI Receive FIFO Not Empty

HOST Command Interrupt

HOST Receive Data Interrupt

HOST Transmit Data Interrupt

DAX Transmit Underrun Error

DAX Block Transferred

DAX Transmit Register Empty

TIMER0 Overflow Interrupt

TIMER0 Compare Interrupt

TIMER1 Overflow Interrupt

TIMER1 Compare Interrupt

TIMER2 Overflow Interrupt

TIMER2 Compare Interrupt

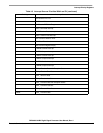

ESAI_1 Receive Data with Exception Status

ESAI_1 Receive Even Data

ESAI_1 Receive Data

ESAI_1 Receive Last Slot

ESAI_1 Transmit Data with Exception Status

ESAI_1 Transmit Last Slot

ESAI_1 Transmit Even Data

Lowest ESAI_1 Transmit Data

Table 4-5 Interrupt Sources Priorities Within an IPL (continued)

Priority Interrupt Source