ESAI Programming Model

DSP56366 24-Bit Digital Signal Processor User Manual, Rev. 4

Freescale Semiconductor 8-9

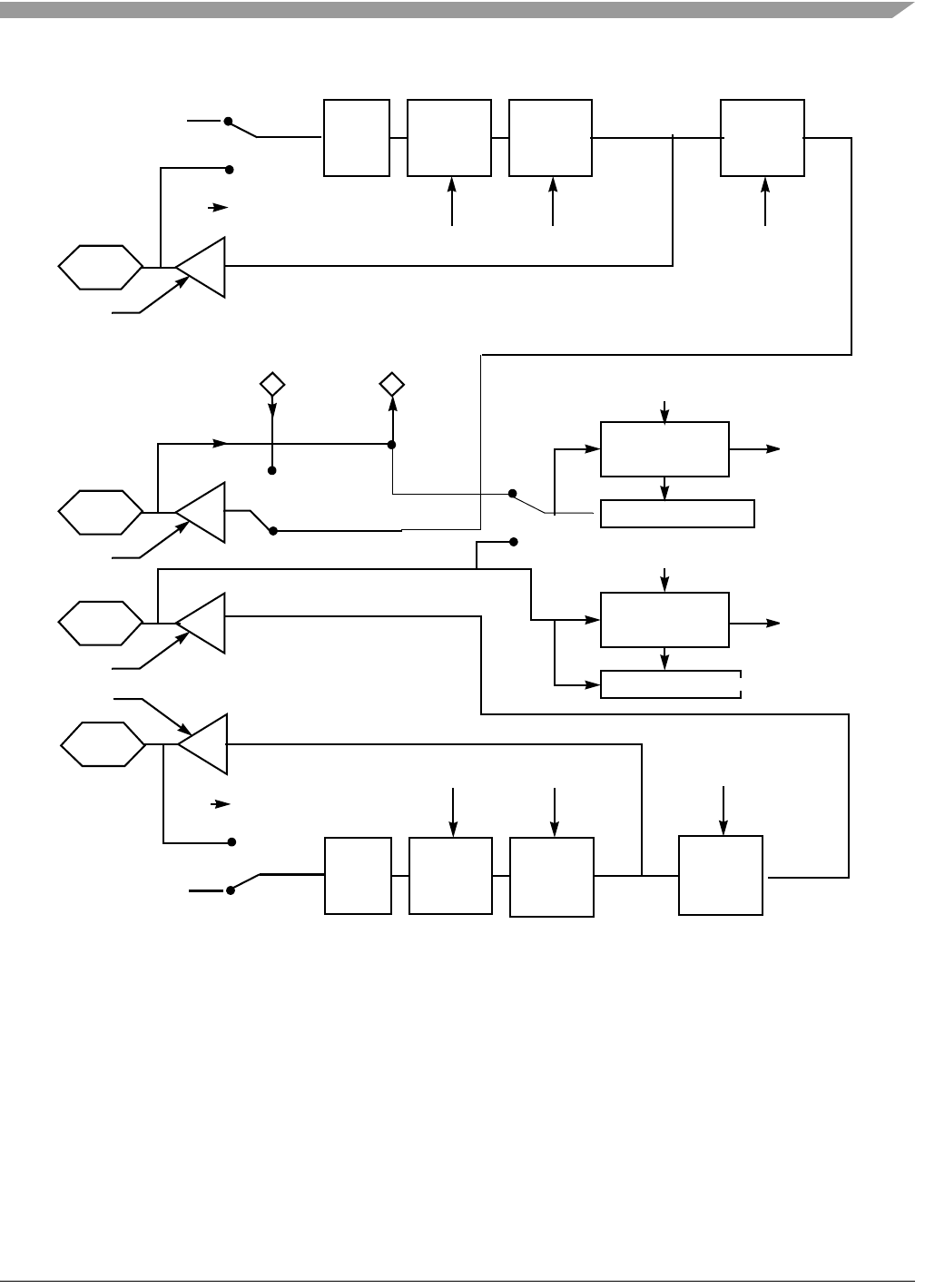

Figure 8-3 ESAI Clock Generator Functional Block Diagram

8.3.1.2 TCCR Transmit Prescaler Range (TPSR) - Bit 8

The TPSR bit controls a fixed divide-by-eight prescaler in series with the variable prescaler. This bit is

used to extend the range of the prescaler for those cases where a slower bit clock is desired. When TPSR

is set, the fixed prescaler is bypassed. When TPSR is cleared, the fixed divide-by-eight prescaler is

FLAG0 OUT

(SYNC MODE)

FLAG0 IN

(SYNC MODE)

SCKR

SCKT

RCKD

TCKD

SYN=1

SYN=0

RCLOCK

TCLOCK

INTERNAL BIT CLOCK

SYN=1

RSWS4-RSWS0

TSWS4-TSWS0

RX WORD

LENGTH DIVIDER

TX WORD

LENGTH DIVIDER

RX SHIFT REGISTER

TX SHIFT REGISTER

DIVIDE

BY 2

PRESCALE

DIVIDE BY

1

OR

DIVIDE BY

DIVIDER

DIVIDE BY

1

TO DIVIDE

BY 256

TPSR TPM0 - TPM7

RX WORD

CLOCK

TX WORD

CLOCK

SYN=0

DIVIDE

BY 2

PRESCALE

DIVIDE BY

1

OR

DIVIDER

DIVIDE BY

1

TO DIVIDE

F

OSC

RPSR RPM0 - RPM7

RHCKD=1

RHCKD=0

HCKR

RHCKD

DIVIDER

DIVIDE BY

1

TO DIVIDE

RFP0 - RFP3

F

OSC

THCKD=1

THCKD=0

HCKT

THCKD

DIVIDER

DIVIDE BY

1

TO DIVIDE

BY 16

TFP0 - TFP3

Notes:

1. F

OSC

is the DSP56300 Core internal clock frequency.

INTERNAL BIT CLOCK