Operating Modes

DSP56366 24-Bit Digital Signal Processor User Manual, Rev. 4

4-4 Freescale Semiconductor

;

do #(PATCH_DATA_END-PATCH_DATA_START+1),PATCH_LOOP

movem p:(r1)+,x0

movem x0,p:(r2)+

nop ; Do-loop restriction

PATCH_LOOP

jsr #M_PROMS ; start ROM code execution

ENDTEST jmp ENDTEST

nop

nop

nop

nop

;

; patch data

;

PATCH_DATA_START

move #5,m0

move #6,m1

move #7,m2

PATCH_DATA_END

;****************************************************************************

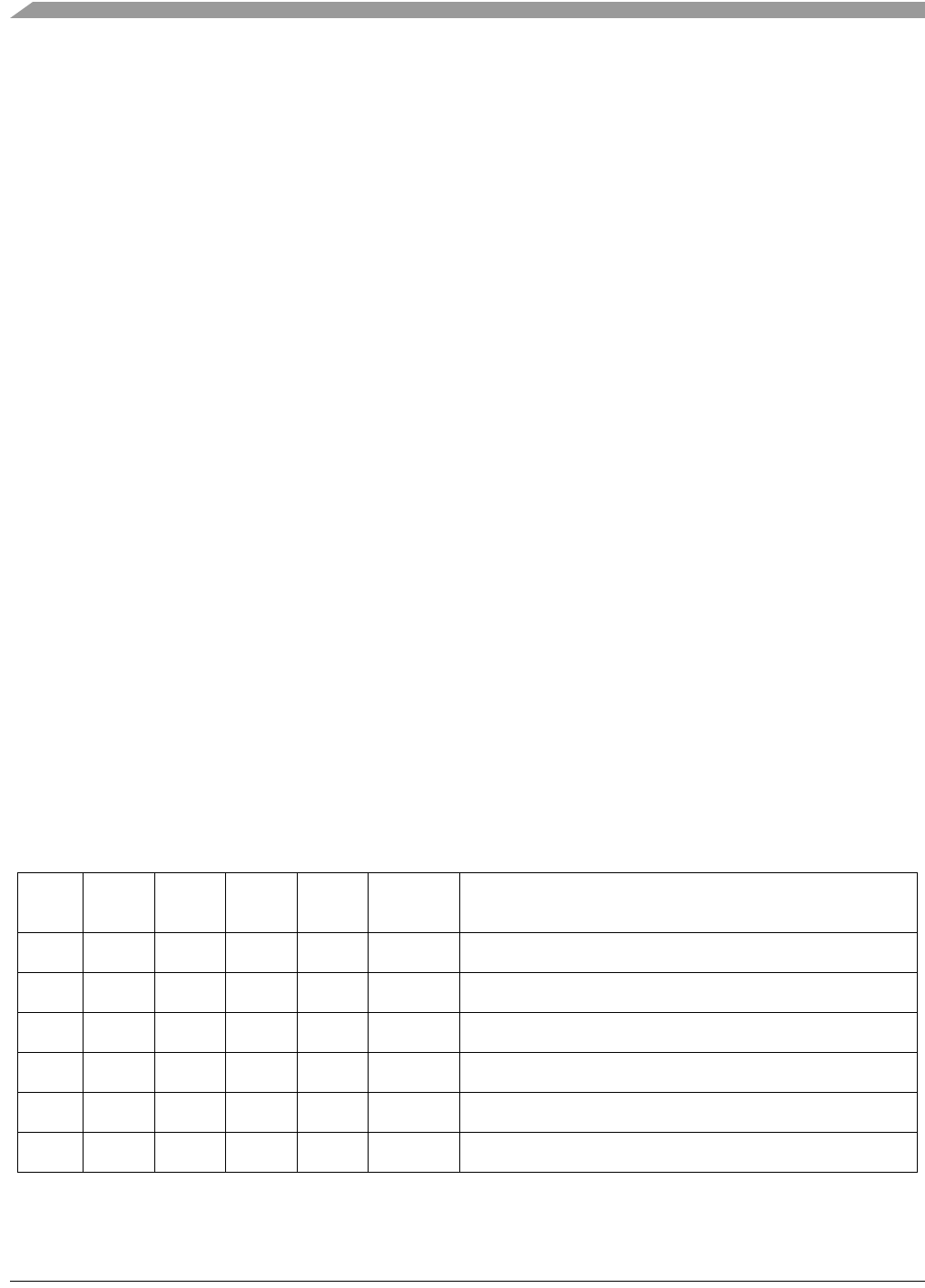

4.3 Operating Modes

The operating modes are defined as shown in Table 4-2. The operating modes are latched from MODA,

MODB, MODC and MODD pins during reset. Each operating mode is briefly described below. Except for

modes 0 and 8, the operation of all other modes is defined by the Bootstrap ROM source code in Appendix

A , "Bootstrap ROM Contents".

Table 4-2 DSP56366 Operating Modes

Mode

MOD

D

MOD

C

MOD

B

MOD

A

Reset

Vector

Description

00000$C00000Expanded mode

10001$FF0000Bootstrap from byte-wide memory

20010$FF0000Jump to PROM starting address

30011$FF0000Reserved

40100$FF0000Reserved

50101$FF0000Bootstrap from SHI (slave SPI mode)