ESAI Programming Model

DSP56366 24-Bit Digital Signal Processor User Manual, Rev. 4

8-22 Freescale Semiconductor

8.3.2.17 TCR Transmit Even Slot Data Interrupt Enable (TEDIE) - Bit 21

The TEDIE control bit is used to enable the transmit even slot data interrupts. If TEDIE is set, the transmit

even slot data interrupts are enabled. If TEDIE is cleared, the transmit even slot data interrupts are

disabled. A transmit even slot data interrupt request is generated if TEDIE is set and the TEDE status flag

in the SAISR status register is set. Even time slots are all even-numbered time slots (0, 2, 4, etc.) when

operating in network mode. The zero time slot in the frame is marked by the frame sync signal and is

considered to be even. Writing data to all the data registers of the enabled transmitters or to TSR clears the

TEDE flag, thus servicing the interrupt.

Transmit interrupts with exception have higher priority than transmit even slot data interrupts, therefore if

exception occurs (TUE is set) and TEIE is set, the ESAI requests an ESAI transmit data with exception

interrupt from the interrupt controller.

8.3.2.18 TCR Transmit Interrupt Enable (TIE) - Bit 22

The DSP is interrupted when TIE and the TDE flag in the SAISR status register are set. When TIE is

cleared, this interrupt is disabled. Writing data to all the data registers of the enabled transmitters or to TSR

clears TDE, thus clearing the interrupt.

Transmit interrupts with exception have higher priority than normal transmit data interrupts, therefore if

exception occurs (TUE is set) and TEIE is set, the ESAI requests an ESAI transmit data with exception

interrupt from the interrupt controller.

8.3.2.19 TCR Transmit Last Slot Interrupt Enable (TLIE) - Bit 23

TLIE enables an interrupt at the beginning of last slot of a frame in network mode. When TLIE is set the

DSP is interrupted at the start of the last slot in a frame in network mode regardless of the transmit mask

register setting. When TLIE is cleared the transmit last slot interrupt is disabled. TLIE is disabled when

TDC[4:0]=$00000 (on-demand mode). The use of the transmit last slot interrupt is described in

Section 8.4.3, "ESAI Interrupt Requests".

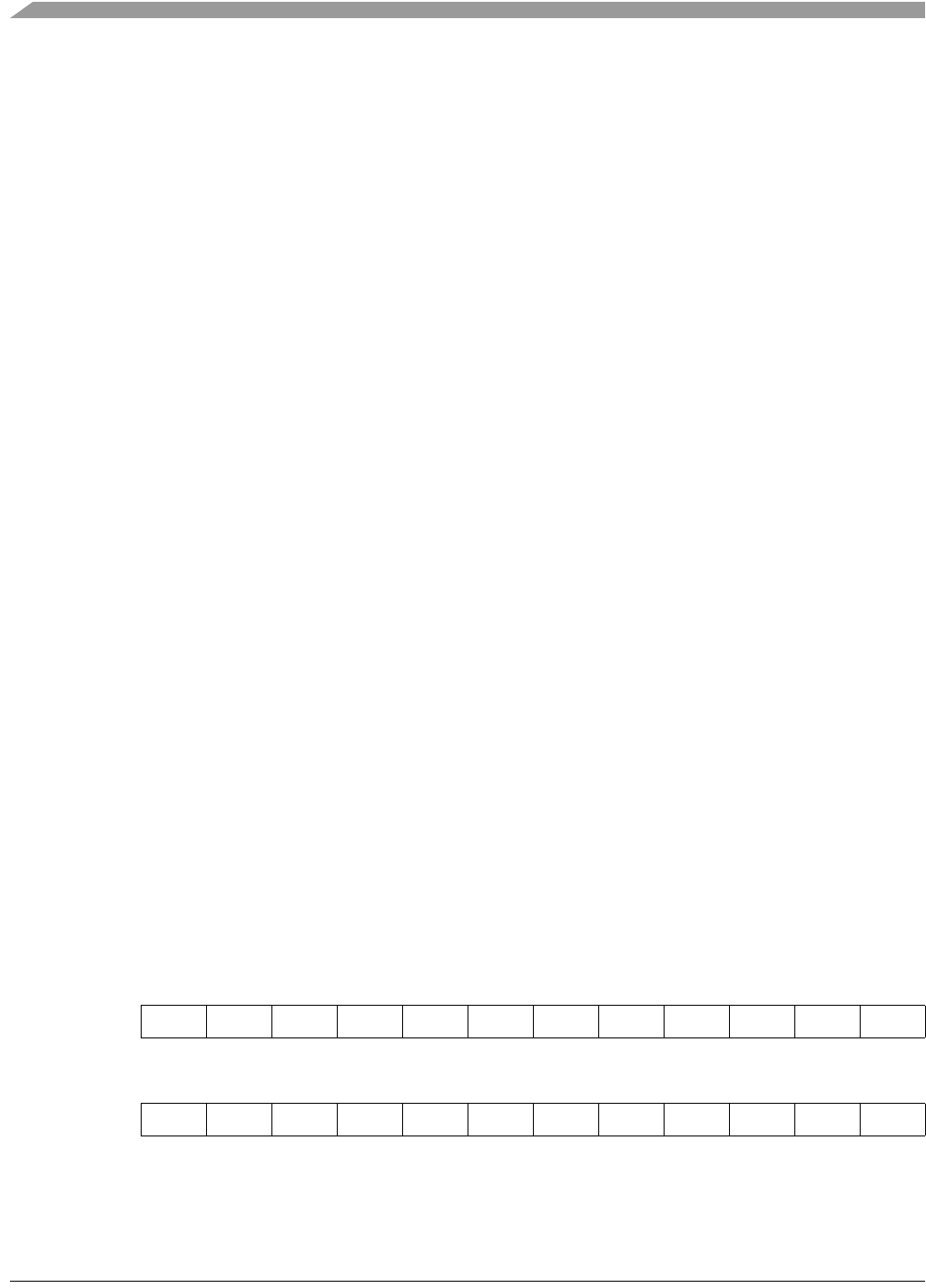

8.3.3 ESAI Receive Clock Control Register (RCCR)

The read/write Receive Clock Control Register (RCCR) controls the ESAI receiver clock generator bit and

frame sync rates, word length, and number of words per frame for the serial data. The RCCR control bits

are described in the following paragraphs (see Figure 8-8).

11109876543210

X:$FFFFB8 RDC2 RDC1 RDC0 RPSR RPM7 RPM6 RPM5 RPM4 RPM3 RPM2 RPM1 RPM0

23 22 21 20 19 18 17 16 15 14 13 12

RHCKD RFSD RCKD RHCKP RFSP RCKP RFP3 RFP2 RFP1 RFP0 RDC4 RDC3

Figure 8-8 RCCR Register