DPSP Convert Double-Precision Floating-Point Value to Single-Precision Floating-Point Value

3-106 Instruction Set SPRU733

Convert Double-Precision Floating-Point Value to Single-Precision

Floating-Point Value

DPSP

Syntax DPSP (.unit) src2, dst

.unit = .L1 or .L2

Compatibility C67x and C67x+ CPU

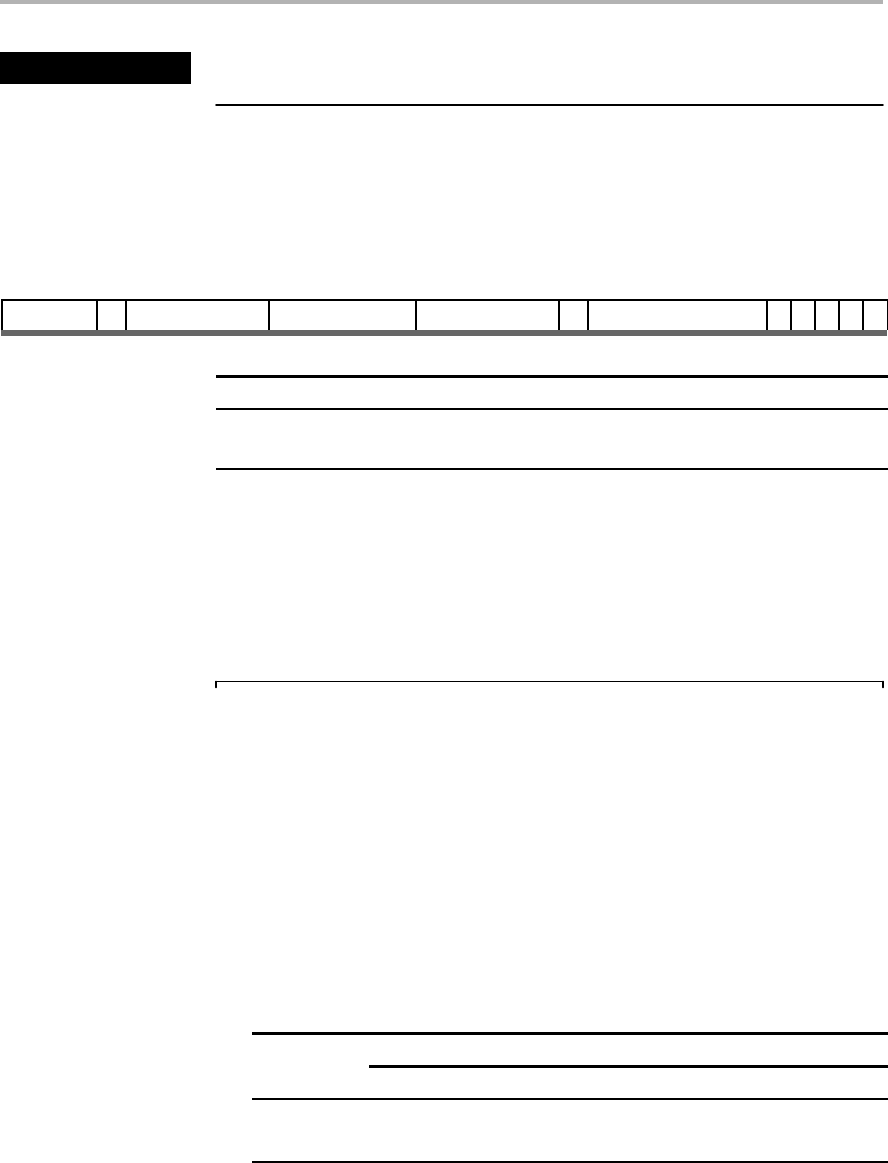

Opcode

31 29 28 27 23 22 18 17 13 12 11 5 4 3 2 1 0

creg z dst src2 0 0 0 0 0 x 0 0 0 1 0 0 1 1 1 0 s p

3 1 5 5 1 1 1

Opcode map field used... For operand type... Unit

src2

dst

dp

sp

.L1, .L2

Description The double-precision 64-bit value in src2 is converted to a single-precision

value and placed in dst. The operand is read in one cycle by using the src2 port

for the 32 MSBs and the src1 port for the 32 LSBs.

Execution if (cond) sp(src2) → dst

else nop

Notes:

1) If rounding is performed, the INEX bit is set.

2) If src2 is SNaN, NaN_out is placed in dst and the INVAL and NAN2 bits

are set.

3) If src2 is QNaN, NaN_out is placed in dst and the NAN2 bit is set.

4) If src2 is a signed denormalized number, signed 0 is placed in dst and

the INEX and DEN2 bits are set.

5) If src2 is signed infinity, the result is signed infinity and the INFO bit is set.

6) If overflow occurs, the INEX and OVER bits are set and the results are

set as follows (LFPN is the largest floating-point number):

Overflow Output Rounding Mode

Result Sign Nearest Even Zero +Infinity −Infinity

+ +infinity +LFPN +infinity +LFPN

− −infinity −LFPN −LFPN −infinity