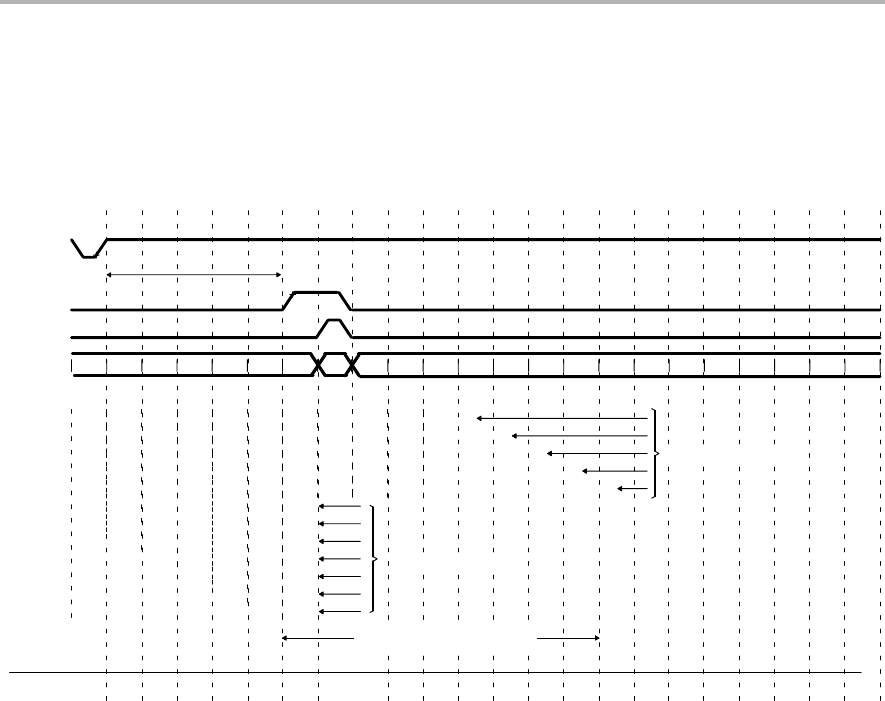

Interrupt Detection and Processing

5-17InterruptsSPRU733

Any pending interrupt will be taken as soon as pending branches are

completed.

Figure 5−4. Nonreset Interrupt Detection and Processing: Pipeline Operation

21 22201917 1816

15

14

000000000

E10

2221

2019

‡

18171615

E1DC

14

1211108976

†

4

5

3

00000

E10

E10

E9

E9

E8

E7

E8

E10

E9

E8

E8

E7

E6

E9

E8

E7

E7

E6

E5

E4

E6

E5

m

0000

E7

E6

E5

E6

E5

E4

E4

E3

E3

E2

E1

E2

E5

E4

E3

E3

E2

E1

E4

E3

E2

E2

E1

E1

DC

DP

DC

DP

PR

PW

DC

DP

PR

21

CPU cycle

IFm

0

External

INTm at

pin

00

IACK

INUM

0

E2

E1

DC

E1

DC

DP

DP

PR

PW

PS

PR

PW

PS

PG

n

n+1

n+2

n+3

n+4

n+5

n+6

DC

DP

PR

PW

PS

PG

Execute

packet

PR

12

11

PWPS

1098

PG

DP

PW

PR

PS

PG

PR

PS

PW

PS

PG

PG

PW

PS

PG

76543

PGn+7

n+9

n+8

n+10

n+11

2

1

ISFP

CPU cycle

0

13

0

E10

13

DP

E9

Cycles 6−14: Nonreset

interrupt processing is disabled

Annulled Instructions

Contains no branch

E8E7E6E4 E5E3E2

†

IFm is set on the next CPU cycle boundary after a 4-clock cycle delay after the rising edge of INTm.

‡

After this point, interrupts are still disabled. All nonreset interrupts are disabled when NMIE = 0. All maskable interrupts are

disabled when GIE = 0.