Subtract Two Double-Precision Floating-Point Values SUBDP

3-261 Instruction SetSPRU733

Notes:

1) This instruction takes the rounding mode from and sets the warning bits

in FADCR, not FAUCR as for other .S unit instructions.

2) The source specific warning bits set in FADCR are set according to the

registers sources in the actual machine instruction and not according to

the order of the sources in the assembly form.

3) If rounding is performed, the INEX bit is set.

4) If one source is SNaN or QNaN, the result is NaN_out. If either source

is SNaN, the INVAL bit is set also.

5) If both sources are +infinity or −infinity, the result is NaN_out and the

INVAL bit is set.

6) If one source is signed infinity and the other source is anything except

NaN or signed infinity of the same sign, the result is signed infinity and

the INFO bit is set.

7) If overflow occurs, the INEX and OVER bits are set and the results are

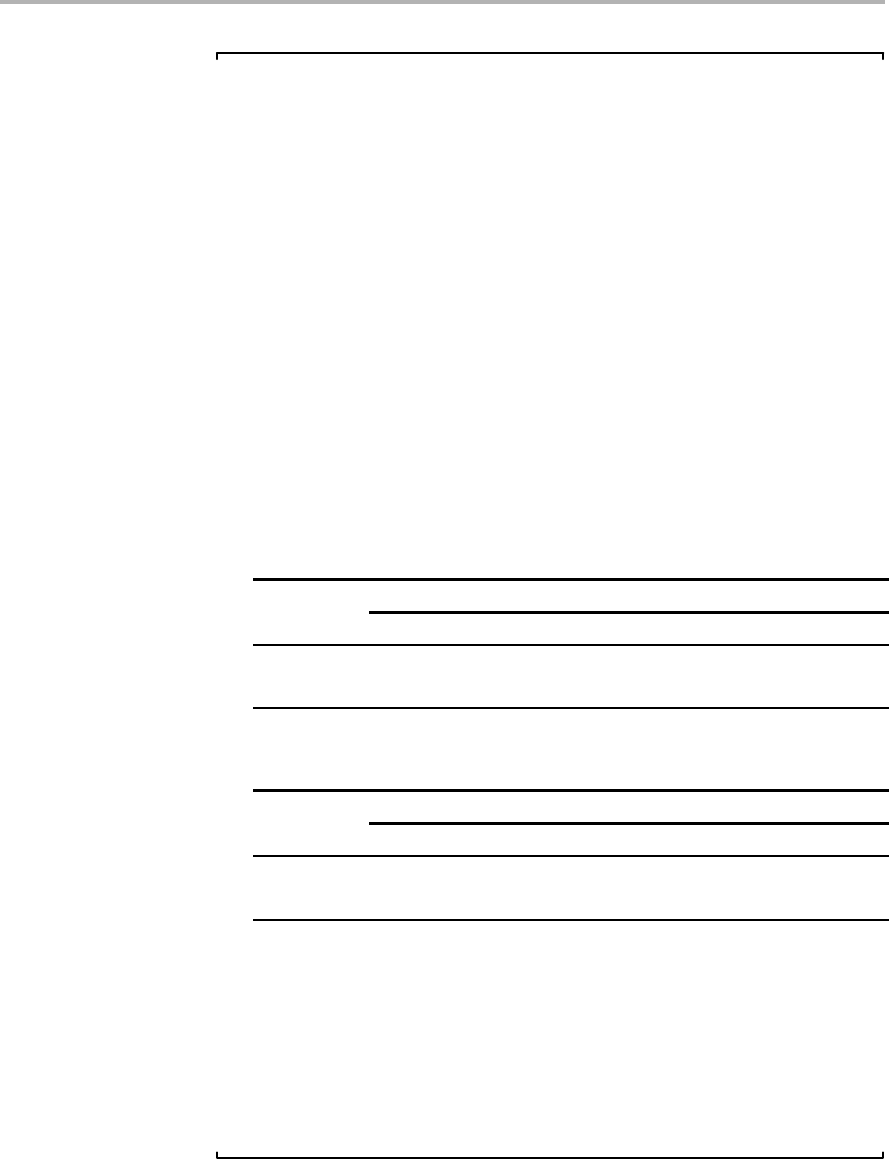

set as follows (LFPN is the largest floating-point number):

Overflow Output Rounding Mode

Result Sign Nearest Even Zero +Infinity −Infinity

+ +infinity +LFPN +infinity +LFPN

− −infinity −LFPN −LFPN −infinity

8) If underflow occurs, the INEX and UNDER bits are set and the results

are set as follows (SPFN is the smallest floating-point number):

Underflow Output Rounding Mode

Result Sign Nearest Even Zero +Infinity −Infinity

+ +0 +0 +SFPN +0

− −0 −0 −0 −SFPN

9) If the sources are equal numbers of the same sign, the result is +0 unless

the rounding mode is −infinity, in which case the result is −0.

10) If the sources are both 0 with opposite signs or both denormalized with

opposite signs, the sign of the result is the same as the sign of src1.

11) A signed denormalized source is treated as a signed 0 and the DENn bit

is set. If the other source is not NaN or signed infinity, the INEX bit is also

set.