Store Word to Memory With a 5-Bit Unsigned Constant Offset or Register Offset STW

3-245 Instruction SetSPRU733

Store Word to Memory With a 5-Bit Unsigned Constant Offset or

Register Offset

STW

Syntax Register Offset

STW (.unit) src, *+baseR[offsetR]

Unsigned Constant Offset

STW (.unit) src, *+baseR[ucst5]

.unit = .D1 or .D2

Compatibility C62x, C64x, C67x, and C67x+ CPU

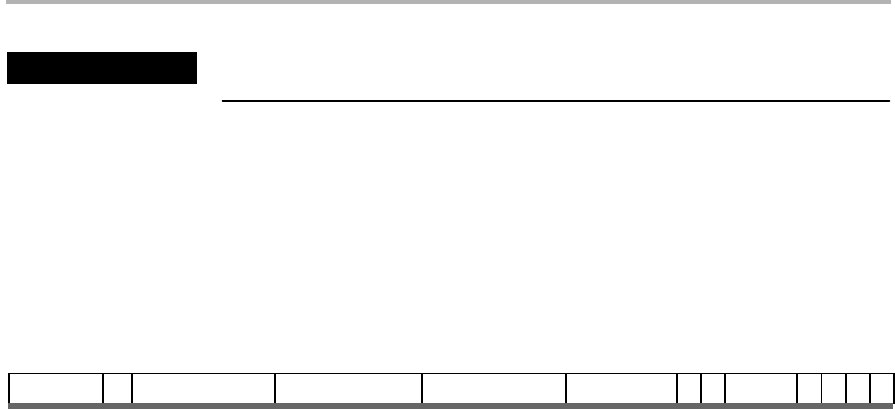

Opcode

31 29 28 27 23 22 18 17 13 12 9 8 7 6 4 3 2 1 0

creg z src baseR offsetR/ucst5 mode 0 y 1 1 1 0 1 s p

3 1 5 5 5 4 1 1 1

Description Stores a word to memory from a general-purpose register (src). Table 3−11

(page 3-33) describes the addressing generator options. The memory

address is formed from a base address register (baseR) and an optional offset

that is either a register (offsetR) or a 5-bit unsigned constant (ucst5).

offsetR and baseR must be in the same register file and on the same side as

the .D unit used. The y bit in the opcode determines the .D unit and register

file used: y = 0 selects the .D1 unit and baseR and offsetR from the A register

file, and y = 1 selects the .D2 unit and baseR and offsetR from the B register

file.

offsetR/ucst5 is scaled by a left-shift of 2 bits. After scaling, offsetR/ucst5 is

added to or subtracted from baseR. For the preincrement, predecrement,

positive offset, and negative offset address generator options, the result of the

calculation is the address to be accessed in memory. For postincrement or

postdecrement addressing, the value of baseR before the addition or subtrac-

tion is sent to memory.

The addressing arithmetic that performs the additions and subtractions

defaults to linear mode. However, for A4−A7 and for B4−B7, the mode can be

changed to circular mode by writing the appropriate value to the AMR

(see section 2.7.3, page 2-10).

For STW, the entire 32-bits of the src register are stored. src can be in either

register file, regardless of the .D unit or baseR or offsetR used. The s bit deter-

mines which file src is read from: s = 0 indicates src will be in the A register file

and s = 1 indicates src will be in the B register file. The r bit should be cleared

to 0.