Parallel Operations

Instruction Set3-18 SPRU733

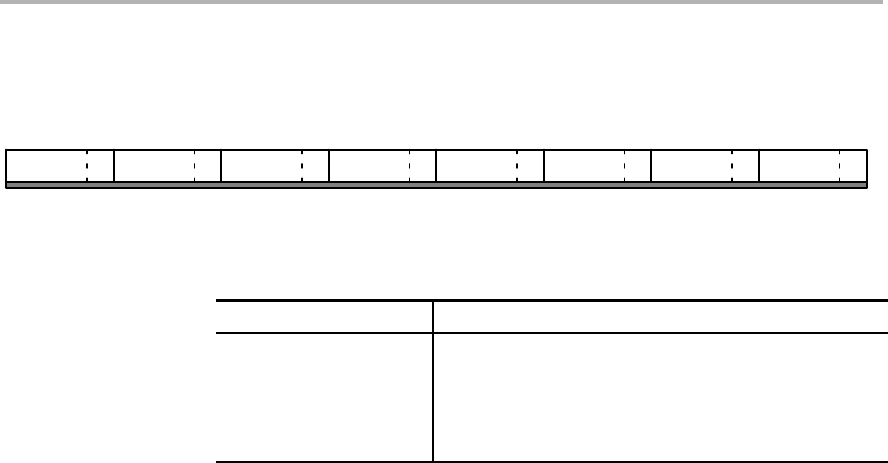

Example 3−3. Partially Serial p-Bit Pattern in a Fetch Packet

This p-bit pattern:

31 0 31 0 31 0 31 0

0011

31 0 31 0 31 0 31 0

0110

Instruction

A

Instruction

B

Instruction

C

Instruction

D

Instruction

E

Instruction

F

Instruction

G

Instruction

H

results in this execution sequence:

Cycle/Execute Packet Instructions

1 A

2 B

3

CDE

4

F G H

Note: Instructions C, D, and E do not use any of the same functional units, cross paths, or

other data path resources. This is also true for instructions F, G, and H.

3.5.1 Example Parallel Code

The vertical bars || signify that an instruction is to execute in parallel with the

previous instruction. The code for the fetch packet in Example 3−3 would be

represented as this:

instruction A

instruction B

instruction C

|| instruction D

|| instruction E

instruction F

|| instruction G

|| instruction H

3.5.2 Branching Into the Middle of an Execute Packet

If a branch into the middle of an execute packet occurs, all instructions at lower

addresses are ignored. In Example 3−3, if a branch to the address containing

instruction D occurs, then only D and E execute. Even though instruction C is

in the same execute packet, it is ignored. Instructions A and B are also ignored

because they are in earlier execute packets. If your result depends on execut-

ing A, B, or C, the branch to the middle of the execute packet will produce an

erroneous result.