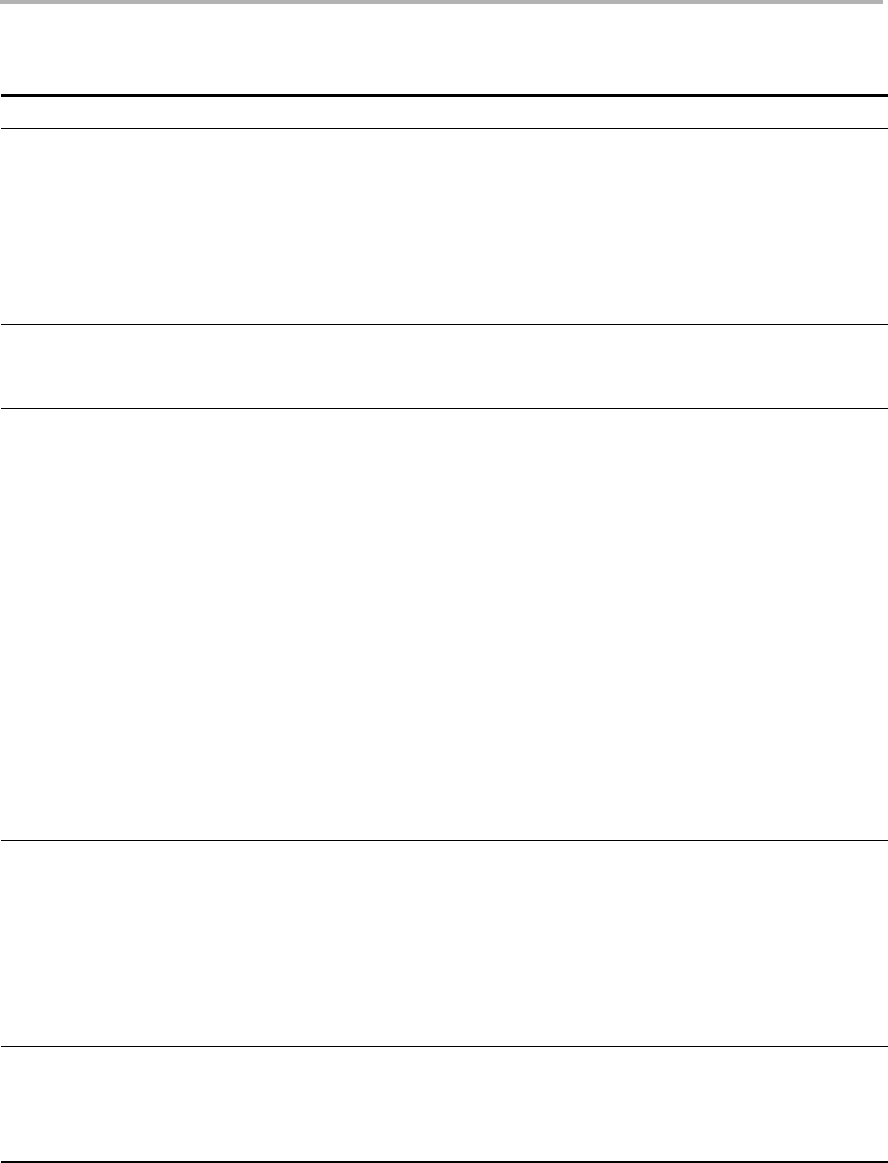

Control Register File

CPU Data Paths and Control2-14 SPRU733

Table 2−7. Control Status Register (CSR) Field Descriptions

Bit Field Value Description

31−24 CPU ID 0−FFh Identifies the CPU of the device. Not writable by the MVC instruction.

0−1h Reserved

2h C67x CPU

3h C67x+ CPU

4h−FFh Reserved

23−16

REVISION ID 0−FFh Identifies silicon revision of the CPU. For the most current silicon

revision information, see the device-specific data manual. Not writable

by the MVC instruction.

15−10 PWRD 0−3Fh Power-down mode field. See Figure 2−5. Writable by the MVC instruction.

0 No power-down.

1h−8h Reserved

9h Power-down mode PD1; wake by an enabled interrupt.

Ah−10h Reserved

11h Power-down mode PD1; wake by an enabled or nonenabled interrupt.

12h−19h Reserved

1Ah Power-down mode PD2; wake by a device reset.

1Bh Reserved

1Ch Power-down mode PD3; wake by a device reset.

1D−3Fh Reserved

9

SAT Saturate bit. Can be cleared only by the MVC instruction and can be set

only by a functional unit. The set by a functional unit has priority over a

clear (by the MVC instruction), if they occur on the same cycle. The SAT

bit is set one full cycle (one delay slot) after a saturate occurs. The SAT

bit will not be modified by a conditional instruction whose condition is false.

0 Any unit does not perform a saturate.

1 Any unit performs a saturate.

8

EN Endian mode. Not writable by the MVC instruction.

0 Big endian

1 Little endian